STM32的时钟源

STM32F103有两种主时钟方案,一个是依靠内部RC振荡器的HSI(内部高速时钟),另一个是HSE(外部高速时钟)。

内部高速时钟源(HSI)

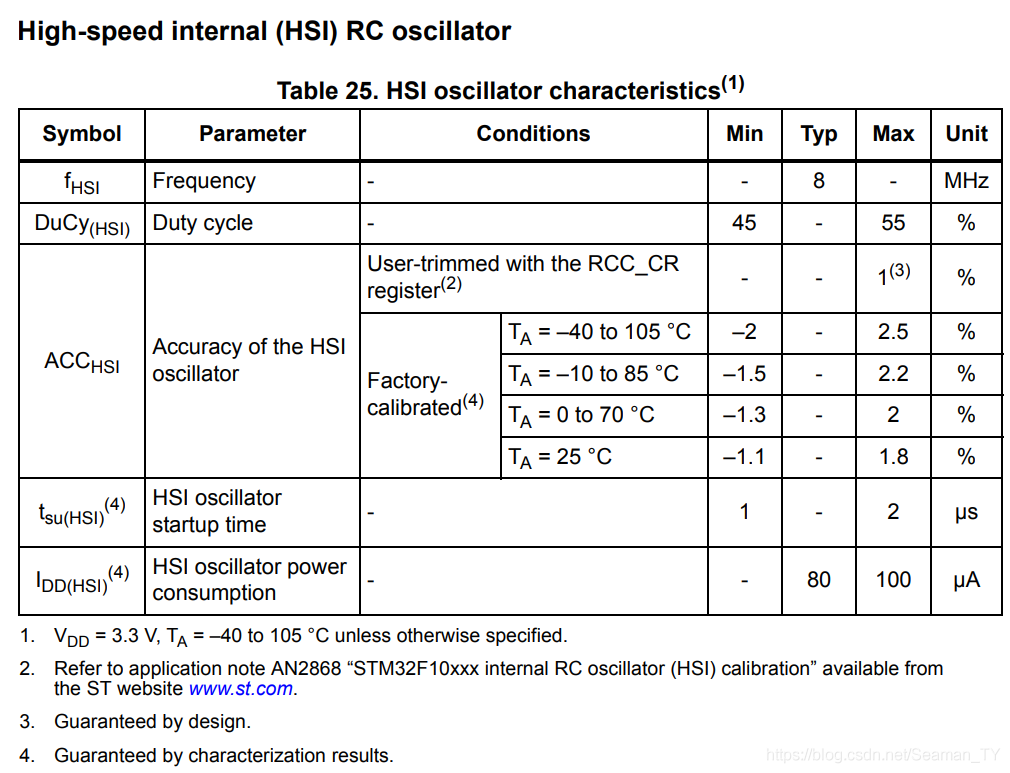

看数据手册,内部的HSI是由ST出厂时校准过的,但是精度并不高,在0到70℃下误差范围达到 -1.3%到2%,即便是在标准的25℃下,也有 -1.1%到1.8% 的误差(如下图)。

对于高波特率的异步串口通讯,或者需要高精度定时的场合(如:需要跑积分算法的时候),用HSI就有隐患,甚至根本达不到设计要求。

外部高速时钟源(HSE)

为了更高的时钟精度,就要用HSE做主时钟源,起码做到30ppm还是很容易的。无源晶振相对便宜一些,要求不是非常高的话也足够了。

对于外部无源晶振,需要做一些匹配工作。当然,直接baidu一个原理图,啥也不想,直接照着抄也可以运行。但是这样的设计,批量生产会不会出问题?某些特定环境下会不会崩溃?系统稳定性会不会很低?……都是未知数。这就是给自己的设计埋下隐患,说不定什么时候就崩了。

所以还是来看看怎么匹配吧–

就以 STM32F103 和 晶技HC-49SMD 8M 20pF 20ppm 的匹配为例

1. 负载电容匹配

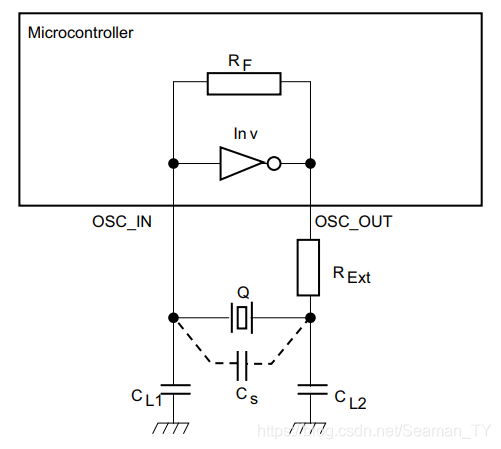

负载电容就是下图中的CL1、CL2,一般取CL1 = CL2,这两个电容和晶体Q构成三点式电容振荡器。

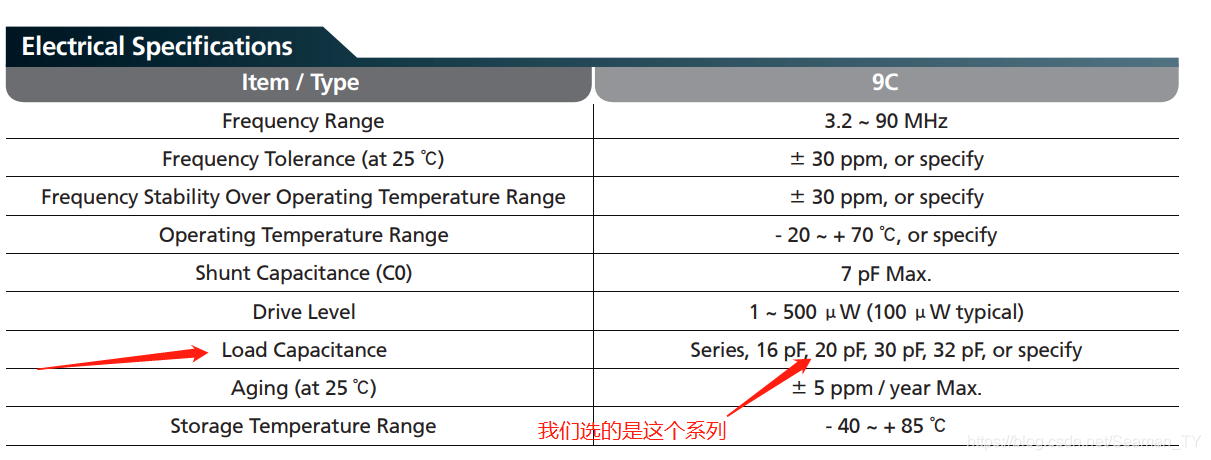

那么要把CL1、CL2跟谁匹配呢?其实就是跟晶振的参数:Load Capacitance匹配,简称CL,从晶振的数据手册可以查到,见下图:

我们选择的是20pF系列的晶振,所以CL = 20pF

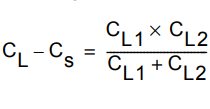

当然我们知道,在电路板走线上还有寄生电容,连接的芯片输入端也有等效电容,这部分也要考虑进去。从ST手册可以查到,STM32F103的晶振输入电容是5pF,而PCB走线的寄生电容一般可以估值3pF到5pF。我们这里就取Cs = 10pF。下面看公式:

由于我们取了CL1 = CL2,公式就可以变为:CL1 = CL2 = 2 * (CL – Cs)

把Cs = 10pF,CL = 20pF带入上面的公式,能求出:CL1 = CL2 = 20pF

因此CL1、CL2均取为20pF。

2. 晶振跨导计算

为了确保晶振能顺利起振,并运行在稳定状态,就得有足够的增益来维持。一般要求就是,单片机的gm比晶振的gmcrit大5倍以上就可以。下面就求一下这个比值,看看是否大于5倍。

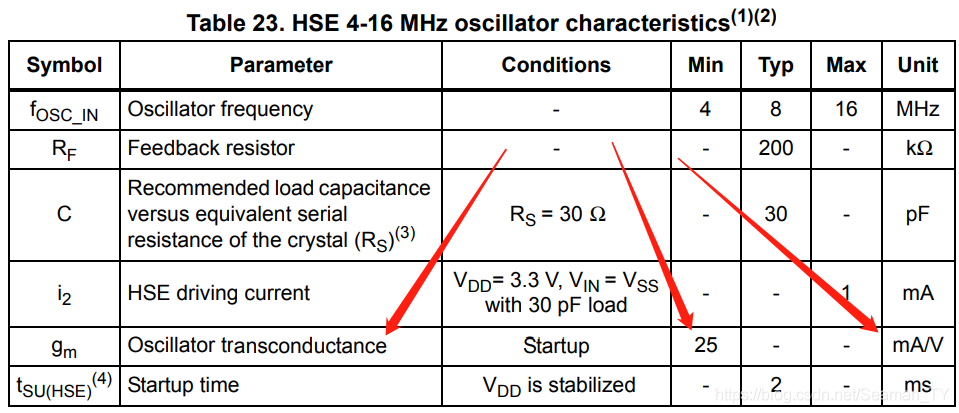

首先看STM32F103手册,可以直接获知:gm = 25mA/V

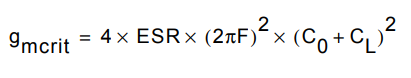

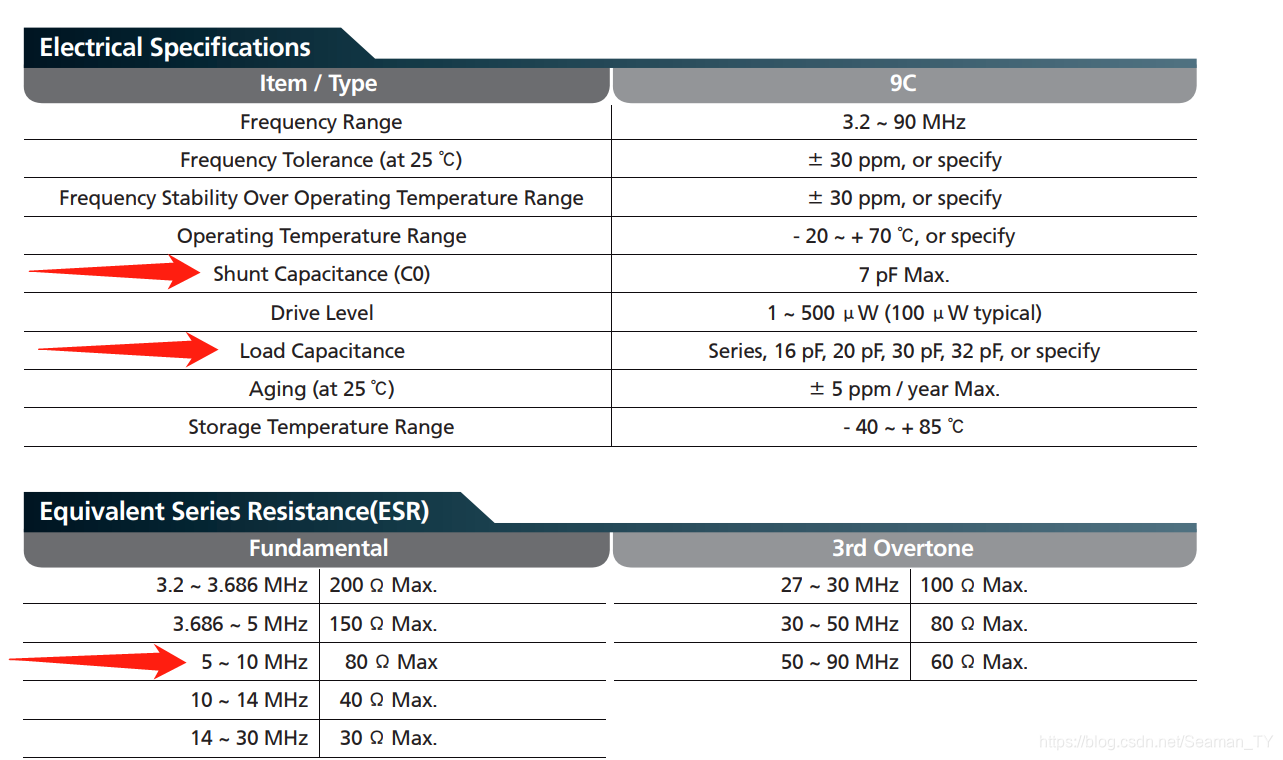

有了gm = 25mA/V,就要用它跟晶振的最小稳定跨导gmcrit相比较。gmcrit是要我们计算一下的:

这里面的几个未知参数的意义是:

ESR——晶振的等效串联电阻,手册里查到

F——晶振的振荡频率

C0——晶振的Shunt Capacitance

CL——晶振的负载电容Load Capacitance

好,下面看晶振的手册,找这几个参数:

F = 8MHz,C0 = 7pF,CL = 20pF,ESR = 80Ω。参数Get√,计算:

gmcrit = 4*80*(2Π*8*10^6)^2*(7*10^-12 + 20*10^-12)^2

gmcrit = 0.1886

现在gm、gmcrit都有了,可以比一下了

比值 = gm/gmcrit = 25/0.1886 = 132

可见,这个比值是132,远大于5倍的最低要求,所以我们选择的晶振是合适的。如果算出来是不合适的,那就要选用更小ESR,更低CL的晶振。其实STM32对于高速晶振的要求不高,但是对于外部低速RTC晶振的要求高一些,选型时要多加留意。

3. 驱动电平DL(Drive Level)

驱动电平其实就是指晶振工作消耗的功率,如果这个功率过大,超过晶振承受能力,则晶振寿命将减少,容易过早失效。晶振的推荐功率,可以在上图(晶振数据手册)中找到,我们选择的这个晶振的DL范围是1到500uW,推荐是100uW。如果实际工作功率过大,就串联一个Rext来限制功耗。实际功耗怎么获得?这个得自己用示波器测量,然后带入ESR计算出来。

4. 反馈电阻Rf (Feedback Resistance)

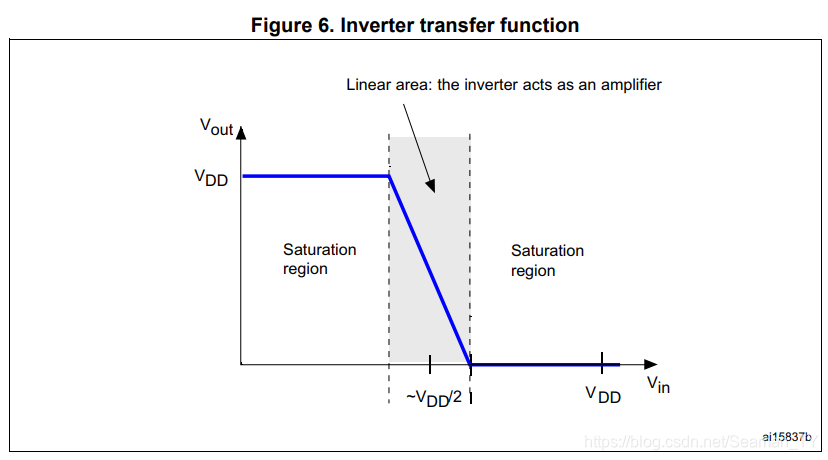

把这个放最后,其实不是因为他没啥用,而是因为ST已经把他集成到芯片里面了,我们不用太多关心这个问题了。这个Rf的作用就是让放大器Vin = Vout,来强制工作在放大区间

总结

以上写的4项,对于STM32F103的高速外部晶振,其实主要考虑“1.负载电容计算”就可以了,这个是直接性影响最大的。

参考:ST应用手册AN2867

版权声明:本文为CSDN博主「Seaman_TY」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/Seaman_TY/article/details/93090532