在设计电路时,涉及到MCU或者CPU以及其他一些时钟电路时,都会有晶振的存在,这些电路都有一个特性,它们都是依赖时钟信号运行的。晶振就是电路心脏,心脏若不能跳动,电路就无法工作。

当我们设计晶振电路时,会下意识的接上两个电容,之前都是参考电路直接设计,并没有了解这么做的原因,今天就稍微花点时间,简单了解下。原来加的这两个电容是为了构成皮尔斯振荡器,震荡电路有很多种,在单片机设计中,最常用的震荡电路模型就是皮尔斯震荡器。

晶振有一个重要的参数就是负载电容值,还有一个重要的测试指标叫震荡裕量,震荡裕量至少要大于等于1,震荡电路才能正常工作。

一.晶振电容的计算

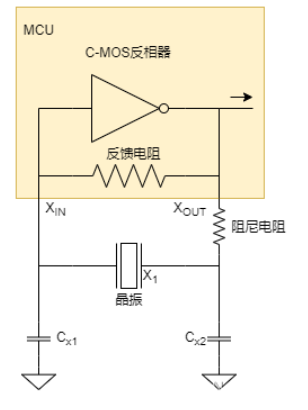

1.1 晶振的拓扑图(皮尔斯震荡电路)

典型的皮尔斯震荡电路通常由C-MOS反相器(在MCU内部)、反馈电阻(多数也在MCU里)、阻尼电阻、外部负载电容和晶体振荡器组成。

1.2 晶振的计算

晶振X1、外部负载电容CX1、CX2构成震荡电路。由于晶振在谐振时呈感性,因此可以看作是电容三点式震荡电路,电路中的X1、CX1、CX2为串联关系,晶振的负载电容计算方式为:

CL = ((CX1*CX2)/(CX1+CX2)) + CS。

式中:

CL:晶振的负载电容;

CS:晶振引脚到MCU之间的引线杂散电容,取值一般为2~5pF。

一般在选择晶振两端的电容时,CX1和CX2相等,因此公式可以简化为:

CL = ((CX1*CX1)/(CX1+CX1)) + CS;

CL = (CX1 / 2) + CS。

从而可以得到CX1为:

CX1 = 2(CL – CS)。

在实际应用中,精确得到CS值比较困难,我们可以通过测量晶振的频率来判断外部电容选的是否合适。当发现晶振的频率偏高时,可以增大电容,反之减小电容。

二.晶振的测试

2.1 测试方法

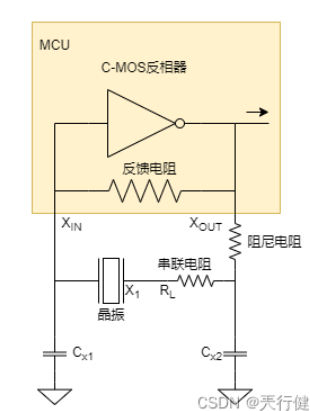

当我们选择好外部电容后,为了判断晶振拓扑是否稳定,可以进行裕量测试,裕量测试常用的方法是负阻测试,测试方法是在晶振支路上串联一个电阻,负阻测试拓扑图如下:

如图所示,测量负阻时,在晶振支路串联一个电阻,阻值的大小取晶振等效电阻(晶振数据手册可以查到)的3~5倍(医疗或者汽车级的应用可以取5~10倍测试),当接入这个电阻后,晶振仍可以正常起振,说明这个晶振拓扑是稳定的。

注意:该串联电阻只在测试时加入,在正式批量生产时,不允许该电阻存在,不要将阻尼电阻和负阻搞混。

2.2 增加裕量的方式

减小外部电容:减小外部电容会增加C-MOS反相器输出端的阻抗,从而增加振荡电路的负阻并增加震荡裕量。在减小外部电容后,需要及时检查晶振的震荡频率是否偏离了需要的值。

减小阻尼电阻:在减小阻尼电阻后,需要检查晶振的激励源是否超过了晶振的额定功率,避免因功率过大导致晶振损坏。

选择内阻小的晶振:在选择晶振时,查看晶振的内阻值,内阻越小,裕量越大。

————————————————

版权声明:本文为CSDN博主「兲行健」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/y15713080686/article/details/125967396