PowerDC是Cadence的一款非常好用的做电源DC仿真的工具,尤其是Powertree功能更是能够大大提高仿真设置的效率。

下面为您介绍如何使用PowerDC进行仿真。

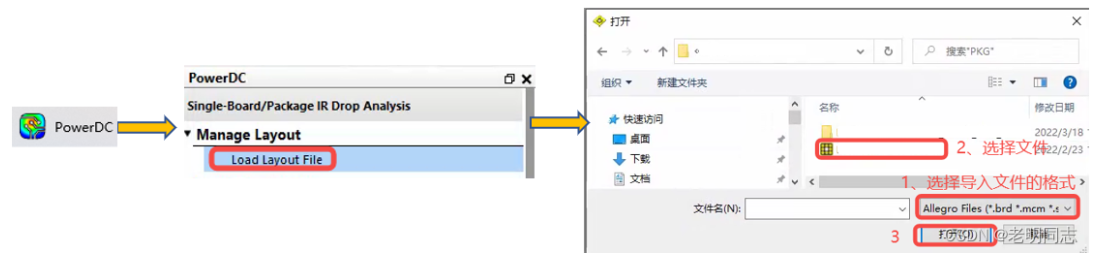

文件导入

首先是运行软件,导入设计文件。这一点不用多说。

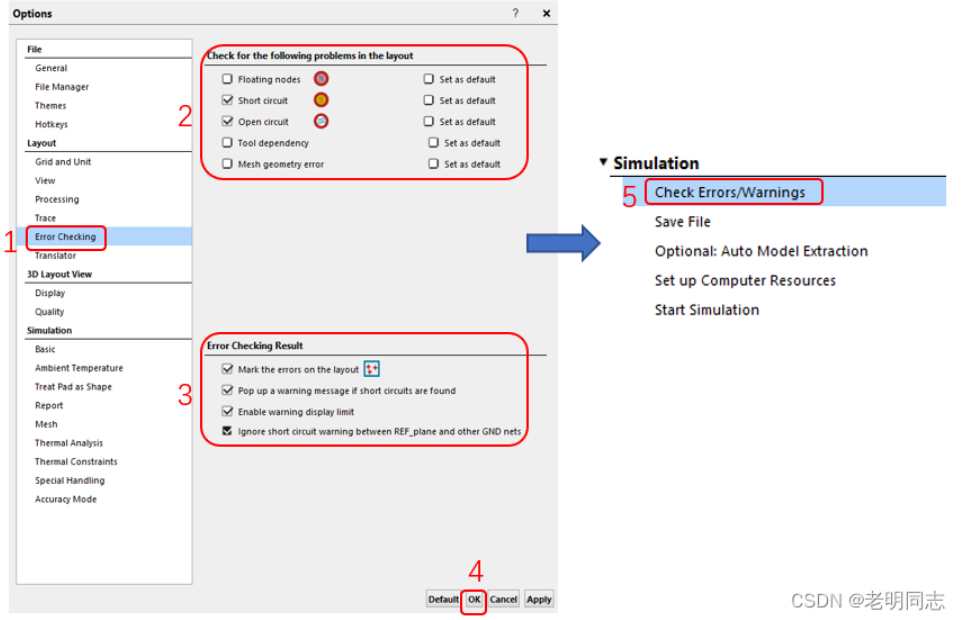

Error check

有的同学习惯导入文件后直接设置,然后开始仿真。我一般先check一下是否存在短路开路的error,没有问题再往下进行。

在Tools –> Options –> Edit Options…中设置,具体操作如下:

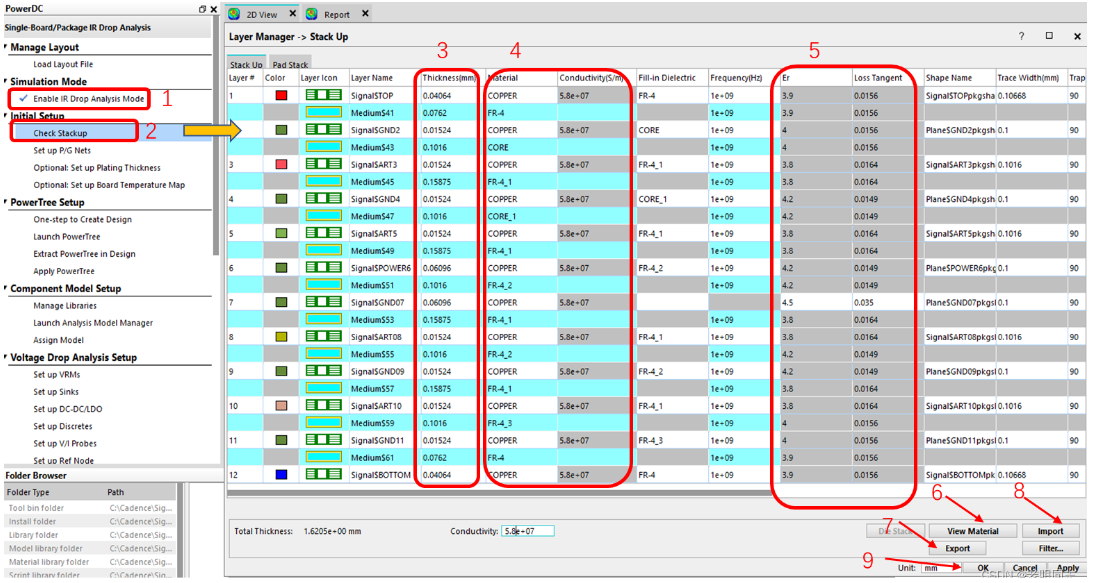

层叠设置

然后进行仿真设置:

1、勾选“Enable IR Drop Analysis Mode”;

2、点击“Check Stackup” ,进行层叠设置。

3、按照实际层叠,设置材料厚度;

4、从材料库中选择材料,铜的电导率设置为5.8e+7。

5、查看材料信息是否正确。

6、如果库中没有相应材料,在View Material中新建材料。

7、导出层叠信息,供后续仿真使用。

8、如果有设置好的层叠也可直接导入。

9、点击“OK”,完成层叠设置。

如下图所示:

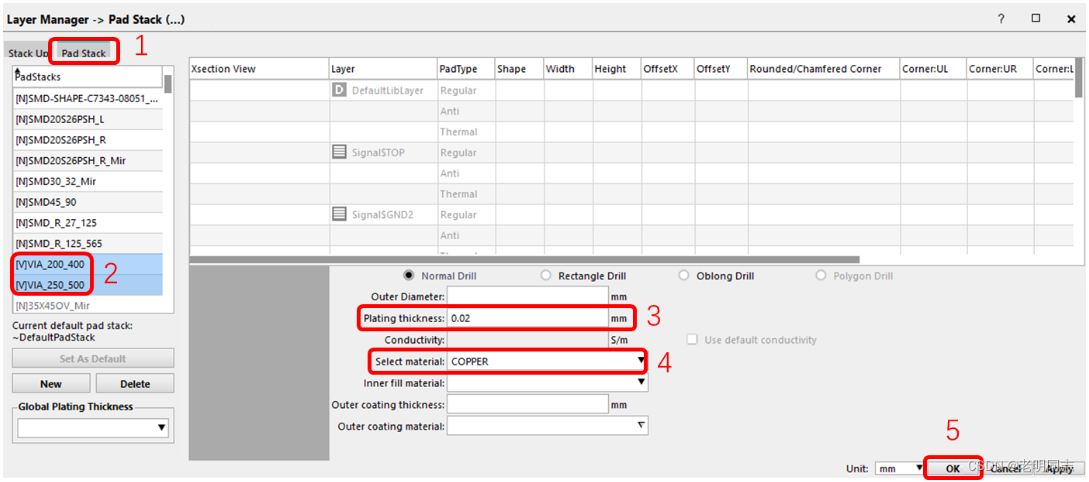

过孔设置

设置完层叠,还要进行过孔设置,主要设置过孔的镀铜厚度。

1、在Layer Manager中选择Pad Stack设置;

2、选择所需设置的所有Via(前面带有[V]标志的);

3、Plating thickness统一设置为20um;

4、材料选择Copper;

5、设置完成,点击“OK”。

powertree设置

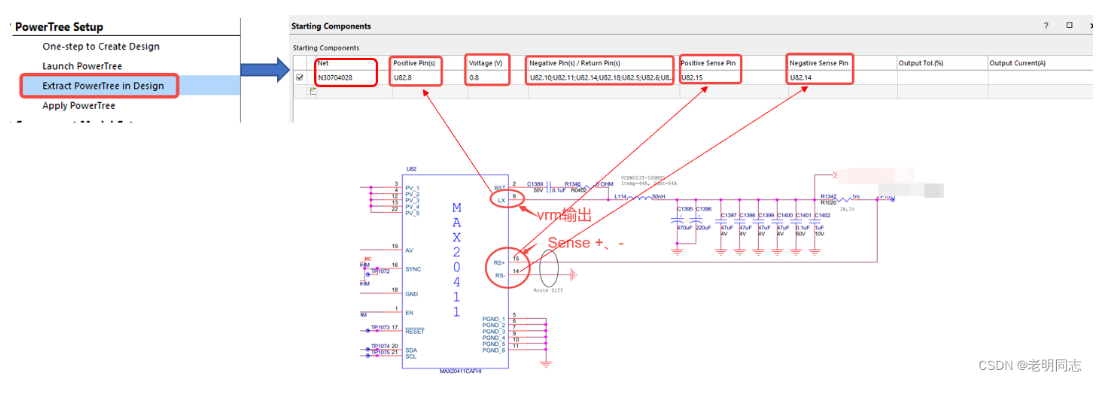

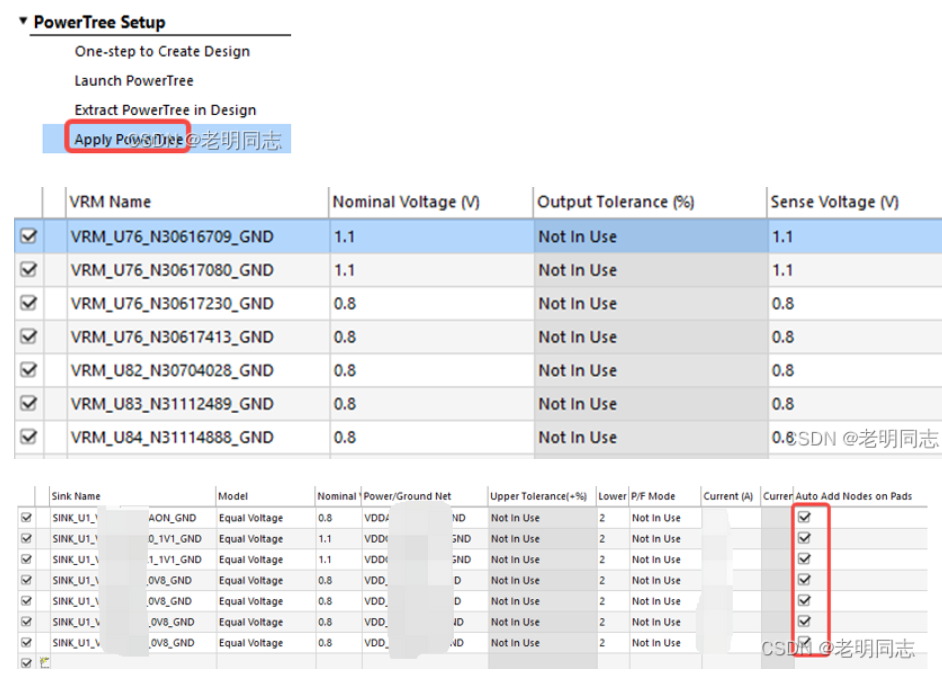

1、在PowerTree Setup栏下,选择”Extract PowerTree in Design”。当然,如果有之前设置好的powertree,也可以选择“Launch Powertree”直接导入。

这里和大家介绍”Extract PowerTree in Design”用法。

2、在弹出的Starting Components 设置中,参考原理图填写Positive Pin(VRM输出的正端)、Positive Sense Pin (反馈线正端)、Negative Sense Pin(反馈线负端),

修改Voltage值,Negative Pin和Net会自动关联。

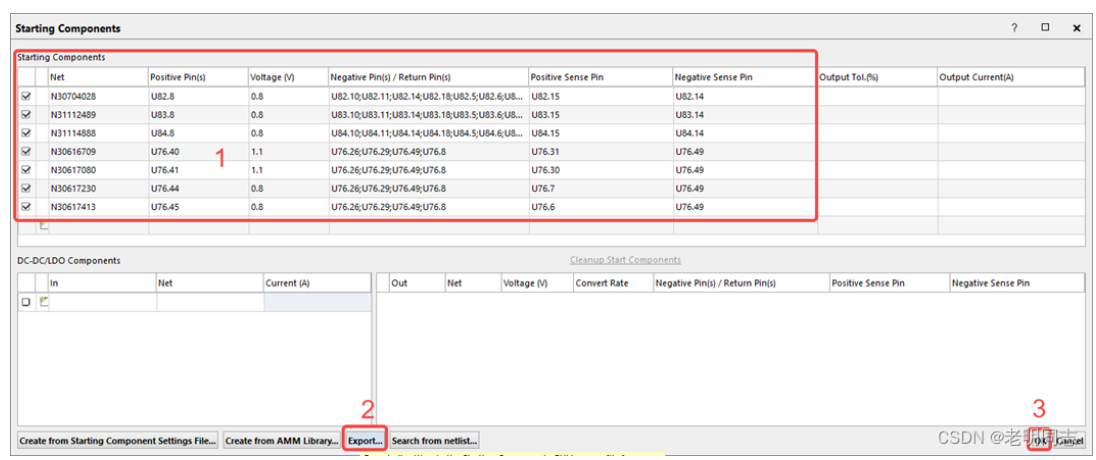

按上面的操作设置好所有需要仿真的Starting Components,如下所示。可以点击“Export”将当前设置导出为.CSV文件,供后续使用;然后点击“OK”,完成Starting Components设置,进入Bulid PowerTree对话框。

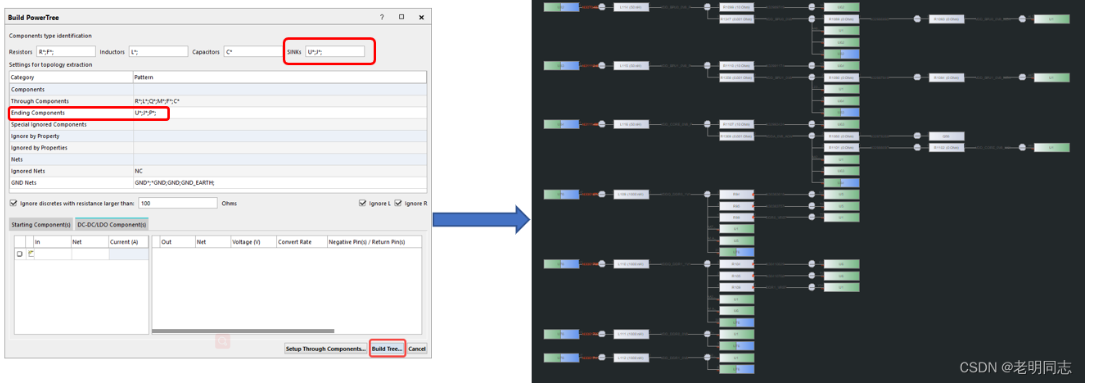

在build powertree对话框中,先检查各种器件位号前缀的设置是否正确,常见的问题是有些客户将芯片的位号定义以“IC”开头,

此时需要在SINKs、Ending Components中增加“IC*”,否则将无法正确识别VRM和Sink芯片。

点击“Build Tree..”,生产如右图所示的PowerTree。

自动生成的PowerTree中可能有一些我们不关注的分支,可以选中之后右键à”Cut off Branches…”,对PowerTree进行简化,简化之后的PowerTree如右图所示。

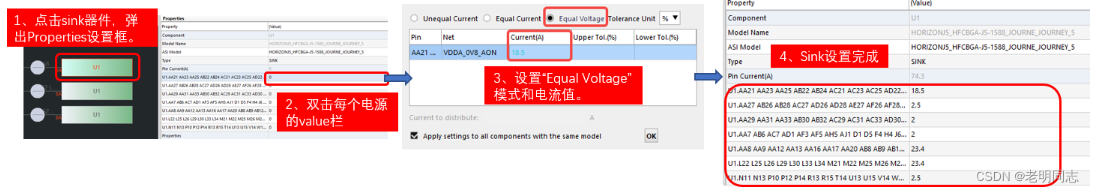

如下所示设置SINK模式和电流值。

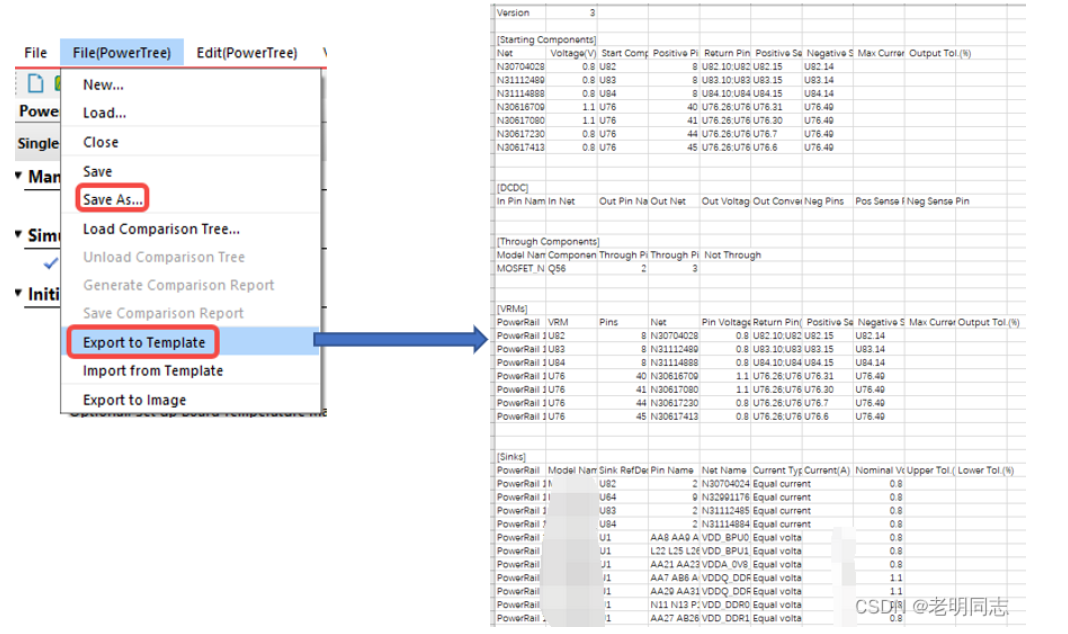

设置完成PowerTree之后可以Save As.. 一个*.pwt格式的PowerTree文件,或者输出一个*.csv的模板,可供迭代仿真使用。

然后点击Apply Powertree,就可以将VRM、Sink、以及一些必要的离散器件设置好了。点击VRM setup和Sink setup检查一下设置是否正确即可。

运行仿真

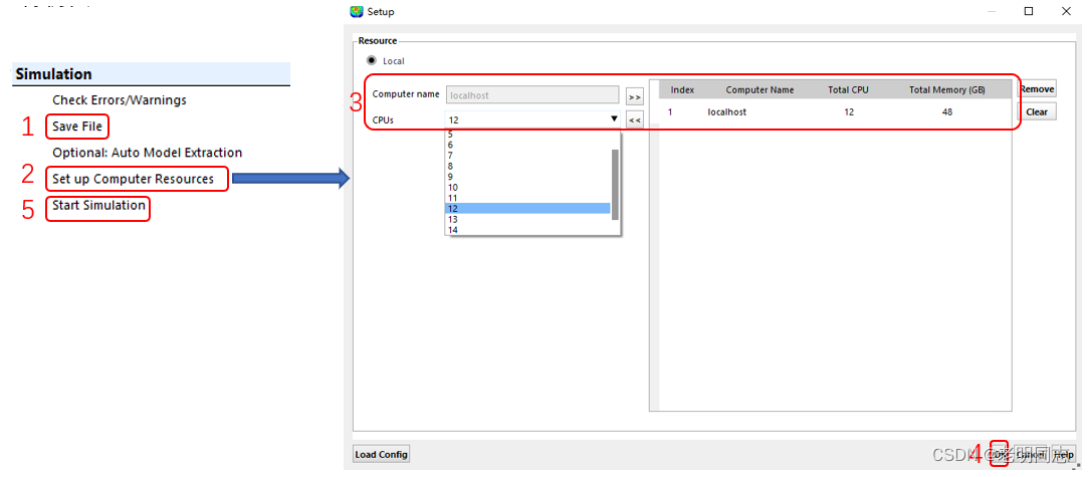

1、保存文件

2、设置计算资源;

3、设置CPU核心数;

4、点击“OK”;

5、运行仿真。

以上就是使用Cadence PowerDC的Powertree进行DC仿真的过程。如果对您有用还请多多支持!

————————————————

版权声明:本文为CSDN博主「老明同志」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_29476769/article/details/128257561