高频传输线中微带线和带状线是常用的走线形式。在某些场合,高速传输线需要由表层穿向PCB内层,则只能通过过孔进行连接。在高频场合下,由于兼顾阻抗匹配,因此过孔的尺寸设计是有一定讲究的。

本文采用过孔将一段表层传输线过渡到内层传输线进行建模,分析一下过孔的仿真模型。暂定PCB的叠层结构如下:四层电路板,PCB板材都是rogers 4350b材质

(备注:实际加工时,是不能这样加工的,

中间需要PP半固化片进行粘接,本文只是提供一下建模思想),每层PCB的铜厚都是1OZ。

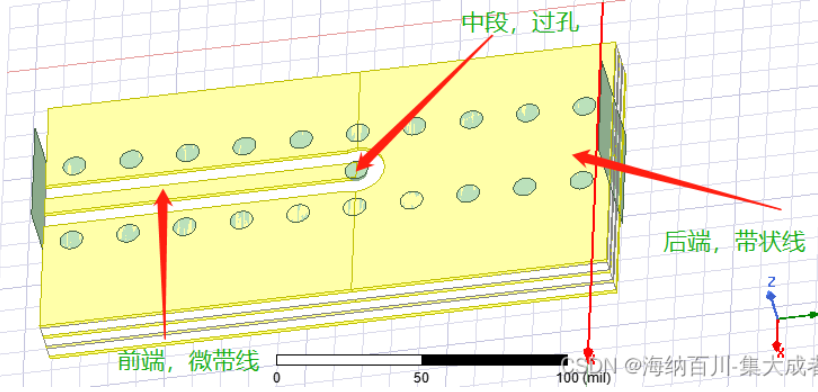

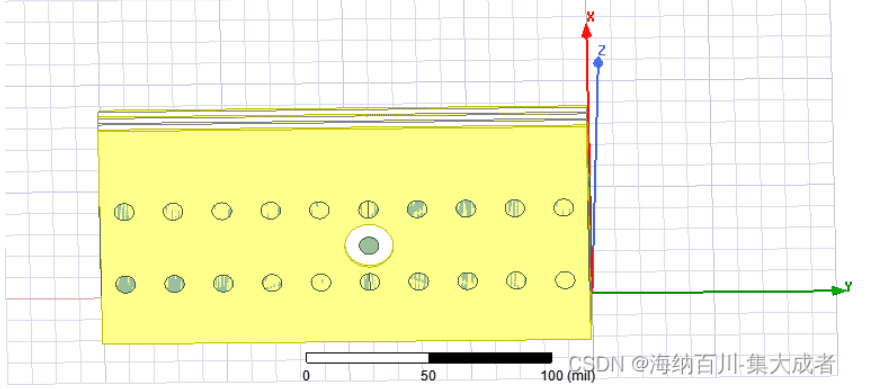

前段:走的是表层的微带线,也有叫共面波导。

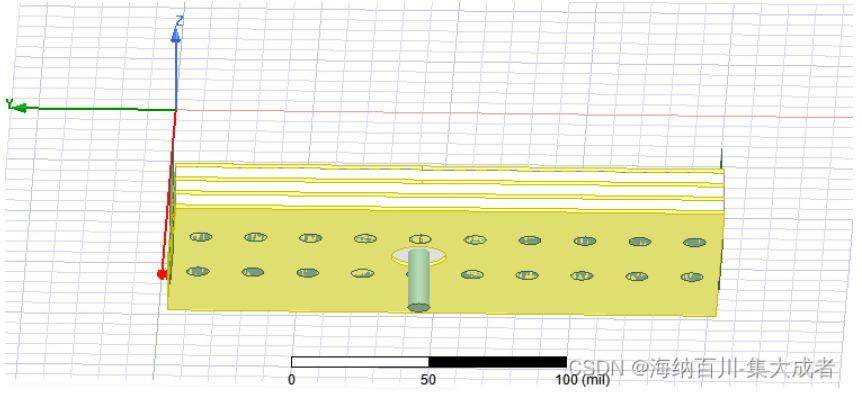

中段:是过孔,将前端传输线与后端的传输线进行连接。过孔目前设计为盲孔形式,过孔只经过表层和第二层。

后段:走的是带状线,长度为从过孔到端口这一段,信号走在第二层,第一层和第三层为信号的参考gnd。剖面图如下:

设计思路:

1. 首先需要仿真一下前段的传输线,确认线宽、线间距。本文最终确定前端的传输线的线宽6.6mil、距表层gnd距离6mil

2. 确认后段传输线的线宽、线间距。本文最终确定后端的传输线的线宽5.3mil,距离gnd的间距为6mil。

3.设计过孔,因为传输线只分布在一、二层,则优先考虑设计盲孔(从一层到二层,后面会介绍为什么不考虑使用通孔结构),一般PCB厂家的过孔最小半径4mil。在此便画一个简单的4mil的圆柱体,圆柱体高度为表层到第二层的厚度,当作过孔(备注:实际的过孔并非实心的结构,部分厂家给的过孔的铜厚在10-20mil,本文直接简化模型,当成实心的)。

最终仿真出来的结果如下:

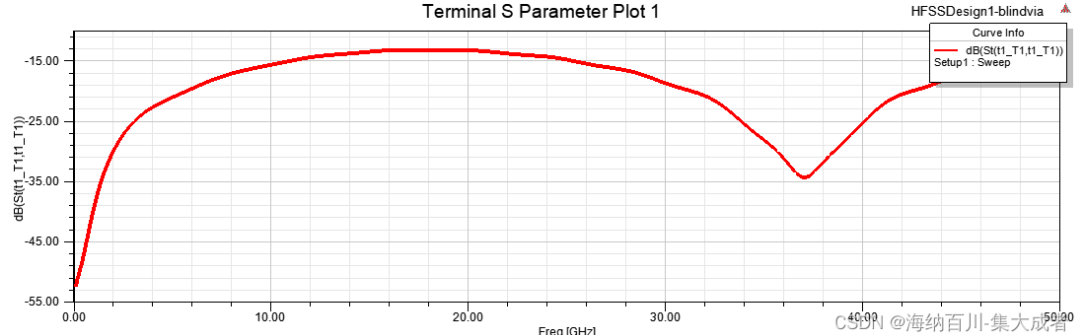

S11:

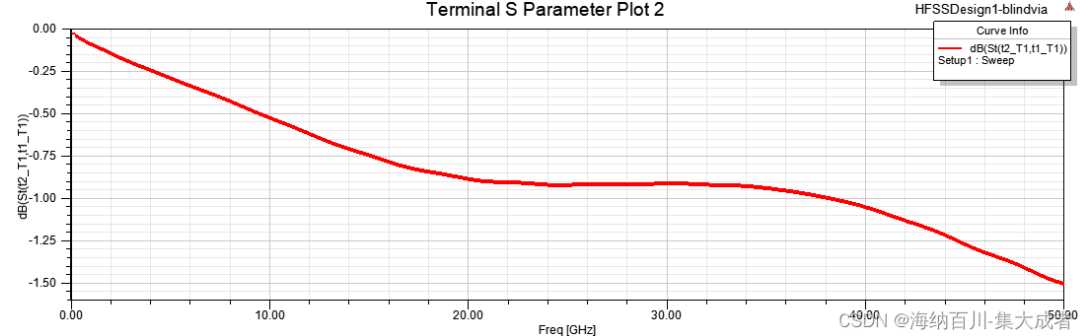

S21:

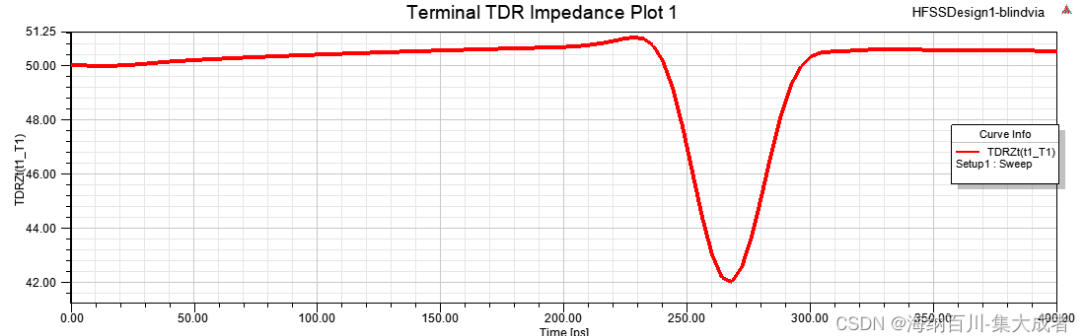

TDR:

从仿真结果可以看出,整体的损耗30G时在0.8左右。其中观察TDR曲线,发现加入过孔后,整条链路的阻抗被拉低到42欧姆左右,出现了阻抗不匹配的情况,因此需要想办法优化过孔。

优化: 因为过孔为盲孔结构,本模型采用的实心铜传导。阻抗肯定会减小,则可以考虑增大过孔与周边铜皮的距离,甚至盲孔下方三四层铜皮的gnd也可以挖掉进行优化阻抗。这部分优化比较费时,在此我只提供一下优化的思路。

问题1:过孔采用盲孔形式,加工起来比较繁琐,那是否可以设计成通孔呢?

为了拿数据进行说话,我在此将通孔也设计成模型2、3,通过对比结果来回答此问题

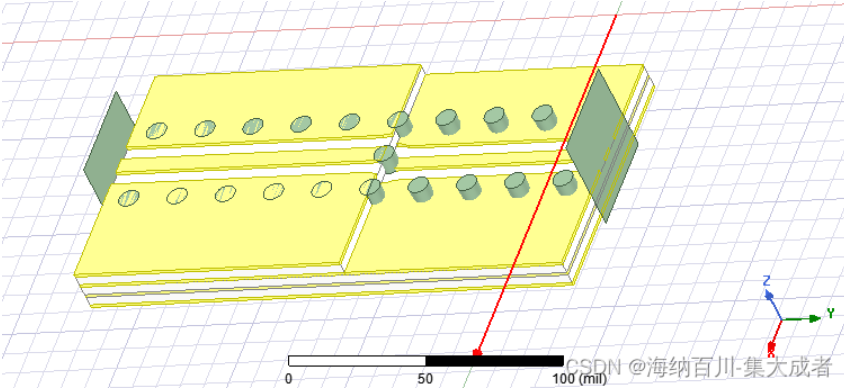

模型2:过孔直接延伸到bottom层,通孔形式。整个板厚较薄,3*4mil+4oz的铜皮厚度

模型3: 由于模型2在实际pcb加工时不可行,板厚太小了,一般我们设计的pcb板厚0.6mm 以上,1mm左右居多,因此模型3将通孔继续延伸到bottom层下方 20mil的空间,保

证整体板厚在1mm左右。(备注:正常情况下,需要将bottom层向下延伸20mil, 在此直接省略了)

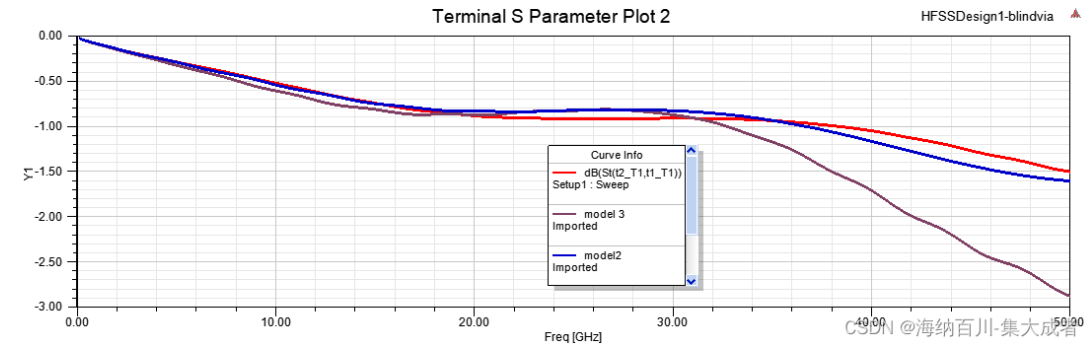

最终三个模型的仿真结果如下:

结论:30G以下,通孔盲孔差别较小;30G以上,通孔的损耗梯度更大些。

因此,能盲孔加工尽量采用盲孔进行设计。插入损耗更小些。纸上得来终觉浅,绝知此事要躬行,吾将上下而求索❗

————————————————

版权声明:本文为CSDN博主「海纳百川-集大成者」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/weixin_42257266/article/details/129657784