一、最小系统的基本组成电路

最小系统主要包括:主芯片,时钟电路,复位电路,电源电路,程序下载口,扩展接口等部分组成。

二、各组成电路详解

(一)主芯片(STM32F103VET6)

1.1 芯片启动模式

1)用户闪存 = 芯片内置的Flash。

2)SRAM = 芯片内置的RAM区,就是内存啦。

3)系统存储器 = 芯片内部一块特定的区域,芯片出厂时在这个区域预置了一段Bootloader,就是通常说的ISP程序。这个区域的内容在芯片出厂后没有人能够修改或擦除,即它是一个ROM区。

在每个STM32的芯片上都有两个管脚BOOT0和BOOT1,这两个管脚在芯片复位时的电平状态决定了芯片复位后从哪个区域开始执行程序:

模式一 BOOT1=x BOOT0=0 从用户闪存启动,这是正常的工作模式。

模式二 BOOT1=0 BOOT0=1 从系统存储器启动,这种模式启动的程序功能由厂家设置。

模式三 BOOT1=1 BOOT0=1 从内置SRAM启动,这种模式可以用于调试。

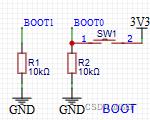

正常使用条件下主要使用模式一和模式二,因此需要使BOOT1引脚接地,BOOT0引脚可以选择接地或者接VCC(3.3V),连接方法如下图所示,BOOT0可以通过按键选择上拉或则下拉,实现模式选择。下面对下拉和上拉电阻进行分析。

1.2 上拉电阻与下拉电阻的使用

(根据B站UP-爱上半导体讲解视频)

1.2.1 上拉电阻的原理与作用

上拉电阻的作用主要有两个:提升电路的驱动能力和将引脚电压钳制在某个值

首先是提升电路的驱动能力:

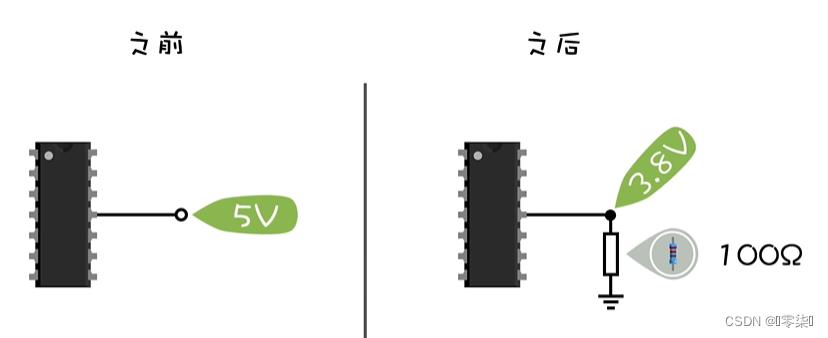

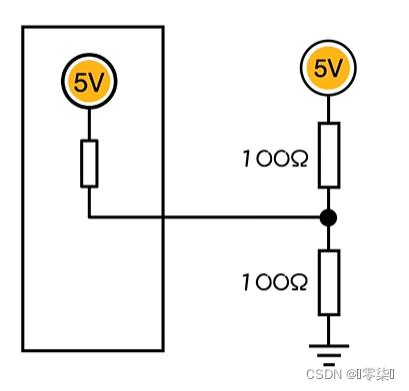

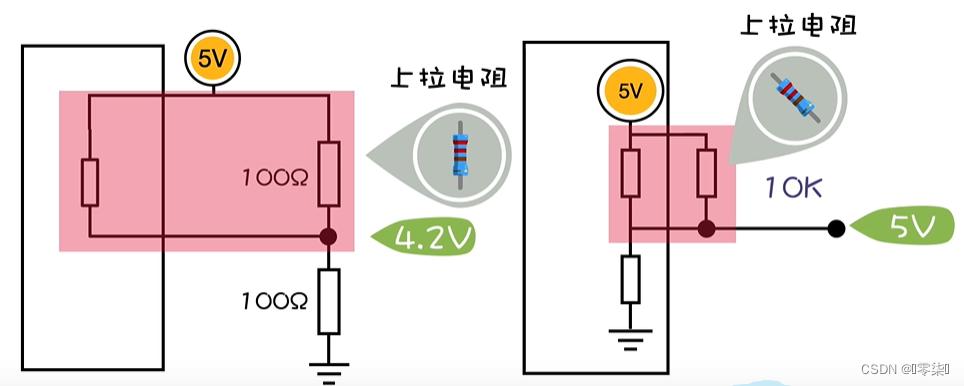

根据实际测试,单片机高电平输出5V电压,在未接负载时,引脚电压等于5V,在外接100欧姆负载之后,引脚电压就下降为3.8V,如下图所示:

在加入10欧姆上拉电阻接VCC(v)之后,引脚原来的3.8V输出变为了4.2V,电压被抬高,提升驱动能力,如下图所示:

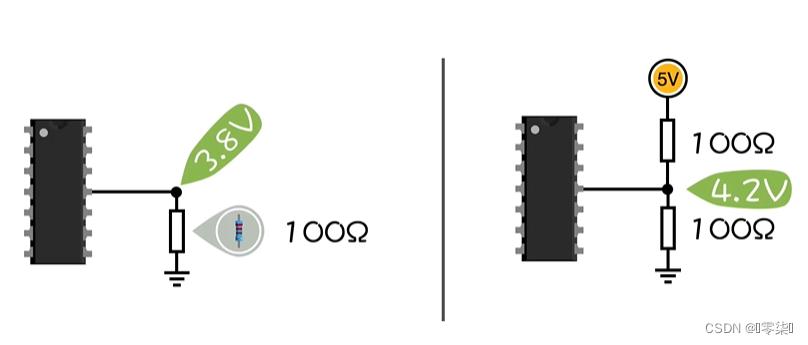

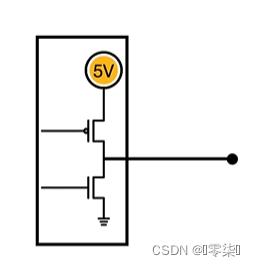

加入上拉电阻可以实现电压抬升是因为单片机引脚的南北与两个MOS管相连,当要求输出高电平时,与VCC相连的MOS导通,与GND相连的MOS 截止,在未接负载时,IO口相当于直接与VCC相连,输出电压约为5V,在接入负载之后,单片机与负载的等效电路如下图所示,MOS管的电阻和外电阻相当于串联,根据串联分压,输出的电压一部分被内阻消耗,一部分提供给外部负载,输出电压就小于5V。

在加入上拉电阻之后等效电路如下图所示,此时内阻与上拉电阻相当于并联,上部分电阻变小,根据串联分压下部分的内阻就会分配到更高的电压,实现电压抬升,此时IO口的驱动能力也将被提高,这就是上拉电阻提升驱动能力的原理。

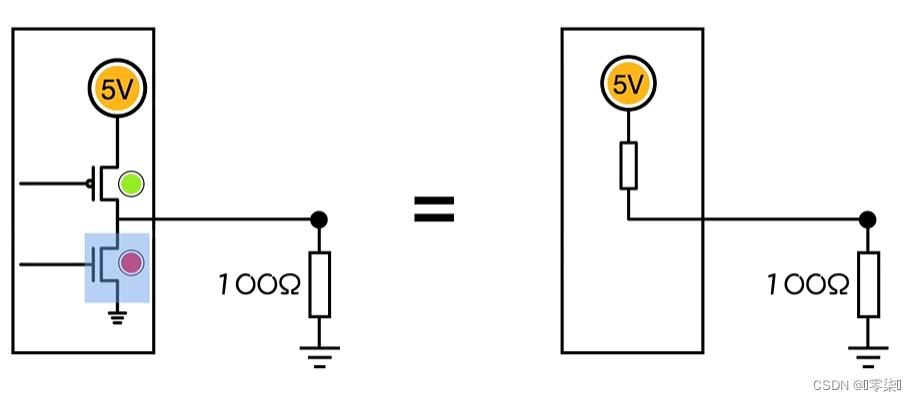

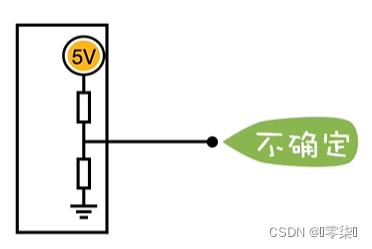

上拉电阻的另外一个作用是钳制电位,在单片机IO处于开漏输出时,上方的MOS管截止,相当于连接了无穷大的电阻,要实现高电平输出,则下方MOS管也必须处于截止状态,此时相当于两个MOS管可以等效为两个无穷大的电阻,电路输出就处于不确定的状态,如下图所示:

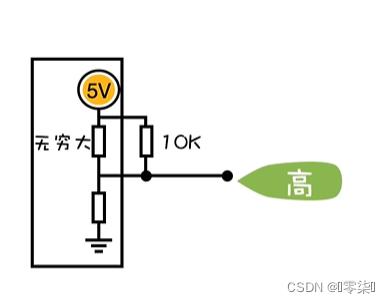

此时我们外接10K上拉电阻,上拉电阻与内部上方电阻并联,等效的最大幅度降低,根据串联分压原理,下方的电阻为无穷大,电源电压几乎全部加在此电阻上,我们测量外部电压时,输出电压近似等于5V,实现电位钳制作用,总之,上拉电阻的原理就是与内阻并联,降低等效电阻,将更多的电压分配给负载,实现电压的抬升或者电位的钳制。

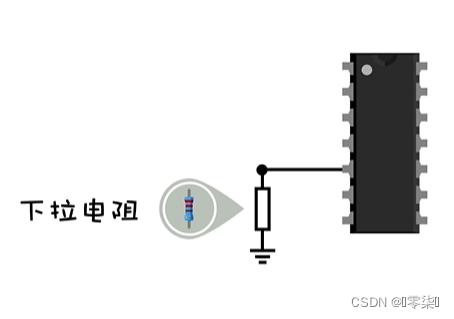

1.2.2下拉电阻的原理与作用

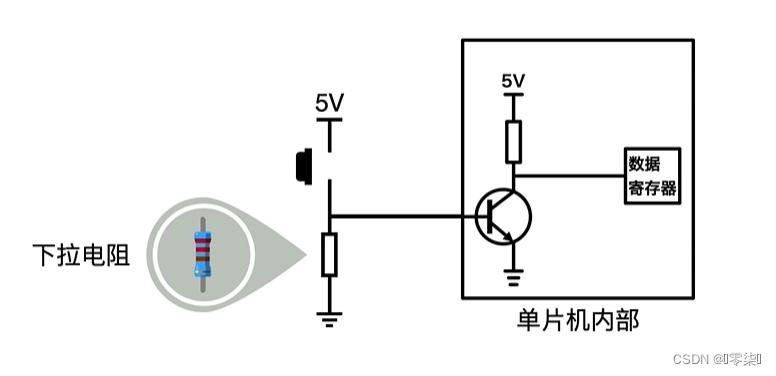

下拉电阻接在单片机的输入引脚与GND之间,如下图所示

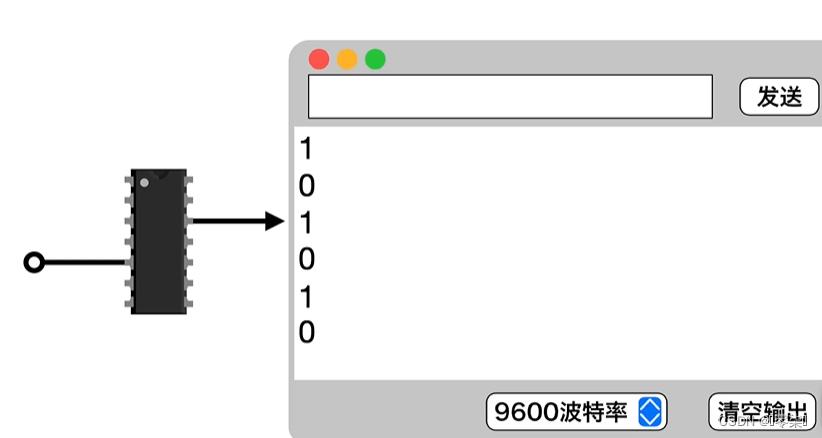

使用单片机的一个数字输入引脚和串口进行仿真,输入脚不接外设,当引脚为高电平时串口输出1,当引脚为低电平时串口输出0,游实验结果可知,输入IO口的输入状态一直在改变,处于不确定的状态。

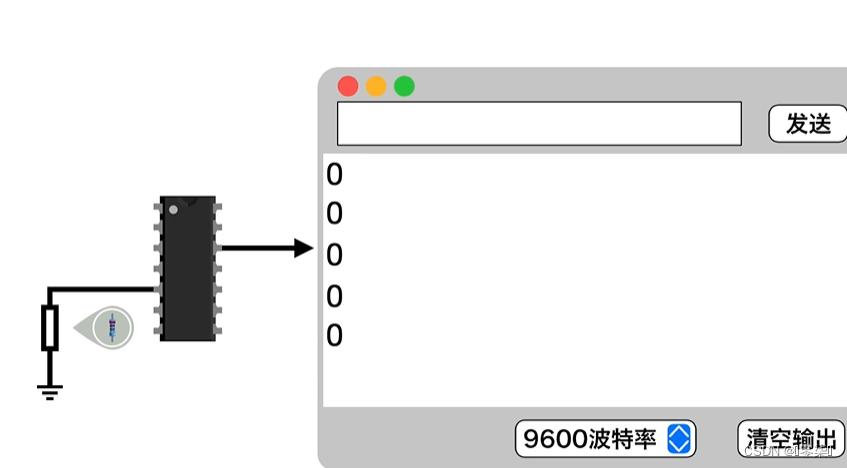

在输入引脚接入下拉电阻之后,实验结果如下图所示,单片机的输入保持在低电平状态,因此下拉电阻可以将输入引脚的电平钳制在特定的状态,为什么下拉电阻可以实现电位钳制呢?

将单片机输入引脚内部进行简化后可以得到等效电路如下图所示,在外加下拉电阻之后,用于内部的三极管截止,不同区域之间存在较大的电阻,外电阻远小于内电阻,因此内部的VCC电压仍然加在内部的三极管上,从IO的电压对于0,下拉电阻将单位钳制在0V,在此处会存在一个问题,为什么不可以将IO口直接与GND相连,这样还可以节省一个电阻?原因是直接将IO与GND相连后,当IO 出入高电平输入时,电流直接通过GND ,不会流进IO,这样就没办法采集到外部的输入信号,因此必须加入下拉电阻,下拉电阻在IO没有输入时保证IO的电平为低,有输入时能够让IO正常采集输入信号。

1.3 主芯片供电

1.3.1 去耦电容

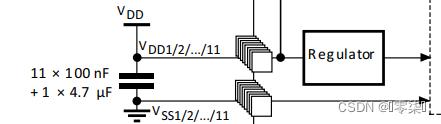

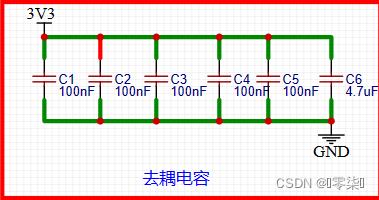

有芯片的数据手册可知,STM32的芯片电源接口之间需要外接去耦电容,假设有n个VSS和VDD,则需要选择n个100nf 和1个4.7uf的电容作为去耦电容,在我们缩写的STM32F103ZET6芯片上有5个VDD/VSS,因此选择5个100nf和一个 4.7uf的电容,原理图如下图所示

去耦电容在进行PCB走线时应该尽可能放在靠近芯片的地方,均匀分布在芯片的电源引脚周围,容值从小到大依次向外排列,在安装去耦电容时在焊盘两侧打孔,接入电源平面与地平面。

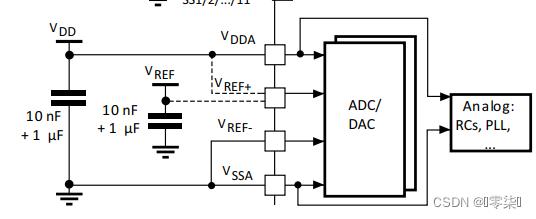

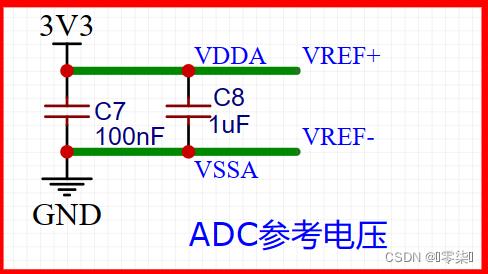

此外除了需要给电源供电意外还需要给ADC提供参考电压,根据手册,需要提供VREF+和VREF-,其中VREF-直接与电源的VSS相连即可,VREF+可以单独提供VREF作为参考电压也可以使用电源的VDD作为参考电压,参考电压之间需要接一个100nf和一个1uf的滤波电容,原理图如下图所示。

(二)复位电路

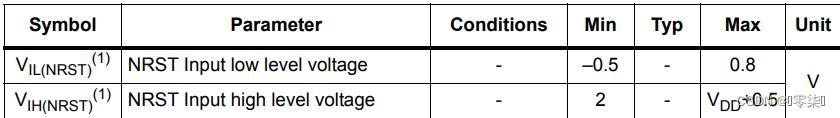

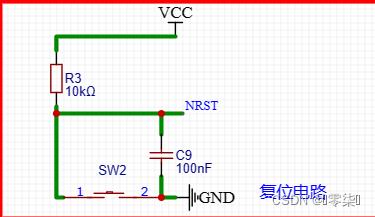

根据官方的数据手册可知,芯片的复位引脚与内部的永久上拉电阻相连,即默认为高电平,当我们提供低电平时芯片会复位。复位低电平的复位(-0.5——0.8)V,高电平为( 2——VDD+0.8) V,默认接电源VCC和GND。

复位电路如下图所示,在默认状态下处于高电平,按下按键后连接到GND,电容C9 的作用是实现按键消抖。

(三)晶振电路

3.1 晶振选择

STM32的外部时钟主要有外部高速时钟和外部低速时钟两部分组成。

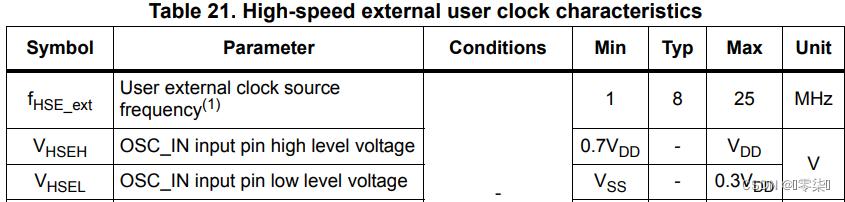

外部高速时钟的频率典型至为8MHz,便于产生72Mhz的时钟频率,在数据手册中提供了具体的选择范围以及时钟引脚的高低电平范围,如下图所示。

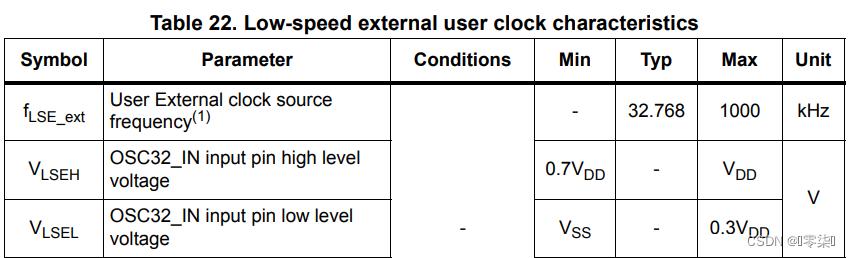

外部的四度时钟使用32.768KHz,根据数据手册课时,最大值一个低于1KHz,选择32.768KHz的目的在于32.768K等于2的十五次方,即32.768KHz经过十五次二分频之后可以得到1Hz,方便使用。具体选择范围如下图所示。

3.2晶振外围电路的搭建

3.2.1 高速晶振的外部电路

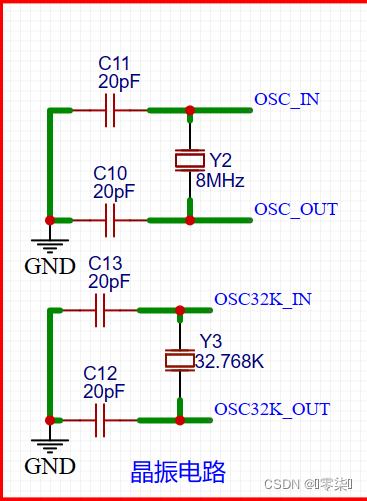

8MHz的晶振电路如下图所示,晶振需要外接两个电容,二电容的选择不是随意的,对于CL1和CL2,建议使用高质量的外置陶瓷电容器,建议使用5pf至25pf范围。CL1和CL2通常大小相同,晶体制造商通常指定的负载电容是CL1和CL2的并联电容。在确定负载电容时,必须包括PCB和MCU引脚电容,10pf可以作为组合引脚和电路板电容的粗略估计。

3.2.2 低速晶振的外部电路

32.768KHz的低速晶振的应用电路如下图所示,同样需要使用两个电容,两个电容推荐使用5-15pf的陶瓷电容,两个电容的大规格相同,具体的电容值可以根据竞争的负载电容值来进行计算,在正常情况下,竞争的负载电容计算公式为CL = CL1 x CL2 / (CL1 + CL2) + Cstray,其中Cstray与电路的pcb走线有关,一般情况下大约为2-7pf,负载电容的计算公式同样适用于高速晶振的负载电容计算,在没有精确频率要求的情况下载推荐范围内选择一个值即可。在选择晶振是尽量使用负载电容低于7pf的晶振,不建议使用负载电容为12.5pf的晶振。

3.2.3 电路设计

高速晶振电路:

负载电容CL=20pf

由:CL = CL1 x CL2 / (CL1 + CL2) + Cstray(10pf),计算出CL1=CL2=20pf,在官方推荐范围内。

低速晶振电路:用于对时钟的精确度没有太高的要求,因此选择使用20pf的电容,节约成本。原理图如下图所示。

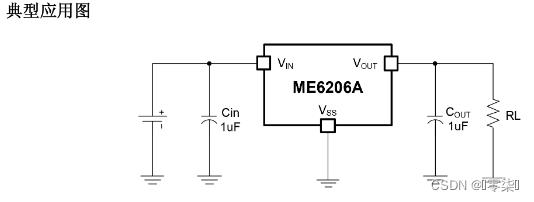

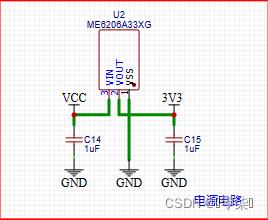

(四)电源电路

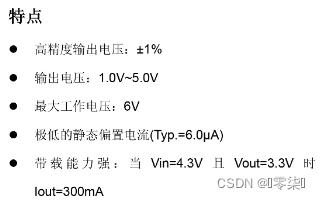

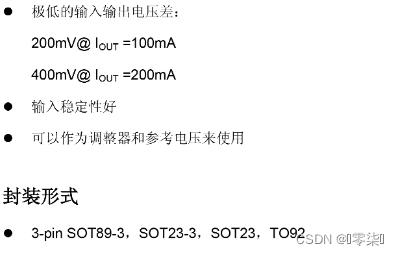

前面章节已经介绍,单片机需要的供电电源为3.3V,外部供电大多数情况是5V或这是12V,因此需要对输入电压进行降压,选择使用微盟电子的ME6206A33-ST023封装的稳压芯片,具体参数和应用电路如下图。

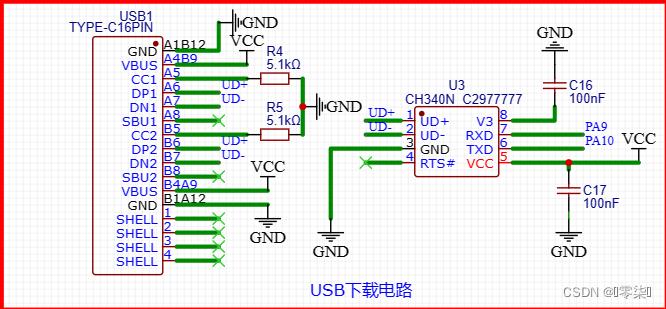

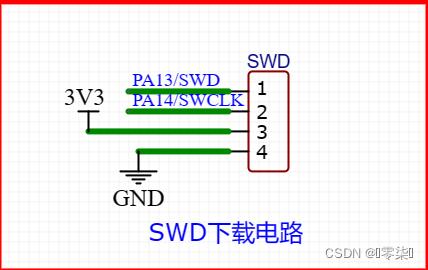

(五)下载电路

为了方便下载调试,设计了SWD下载和USB下载两种方式

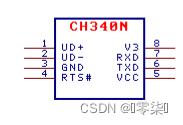

USB下载电路选择使用CH340N芯片,封装如下图所示:

UD+:连接到USB总线的D+数据接口,不需要串联电阻;

UD-:连接到USB总线的D-数据接口,不需要串联电阻;

VCC:电源输入,需要外接100nf的去耦电容;

GND:电源输入GND;

V3:电源为5V输入是需要外接100nf去耦电容然后接地;

RDX::数据输入,接单片机的TX;

TXD:数据输出,接单片机的RX;

16PIN的Type-C接口,引脚功能图如下图所示:

电路原理图如下:

SWDIO下载电路如下图所示:

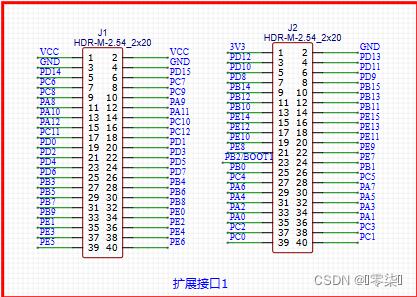

(六)扩展接口

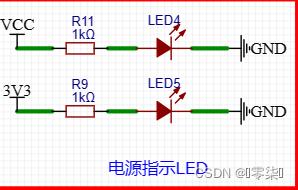

电源指示

扩展IO

原理图设计到此结束啦,不知道能不能实现,还需要布线,PCB打样,测试。

经过几天等待,板子到啦,经过实际测试,板子没问题!

(在此之前都是使用别人的原理图,不知道原理,这次算是根据数据手册自己花了一遍,若有不足,希望各位大佬批评指正,我很乐意继续完善我的最小系统!!)

转自:

https://blog.csdn.net/qq_52111026/article/details/130521860