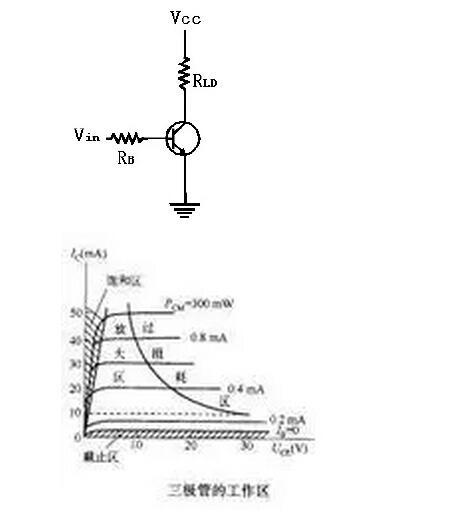

1、开关三极管的基本电路图

负载电阻被直接跨接于三极管的集电极与电源之间,而位居三极管主电流的回路上,输入电压Vin则控制三极管开关的开启(open) 与闭合(closed) 动作,当三极管呈开启状态时,负载电流便被阻断,反之,当三极管呈闭合状态时,电流便可以流通。 详细的说,当Vin为低电压时,由于基极没有电流,因此集电极亦无电流,致使连接于集电极端的负载亦没有电流,而相当于开关的开启,此时三极管乃工作于截止(cut off)区。

同理,当Vin为高电压时,由于有基极电流流动,因此使集电极流过更大的放大电流,因此负载回路便被导通,而相当于开关的闭合,此时三极管乃工作于饱和区(saturation)。

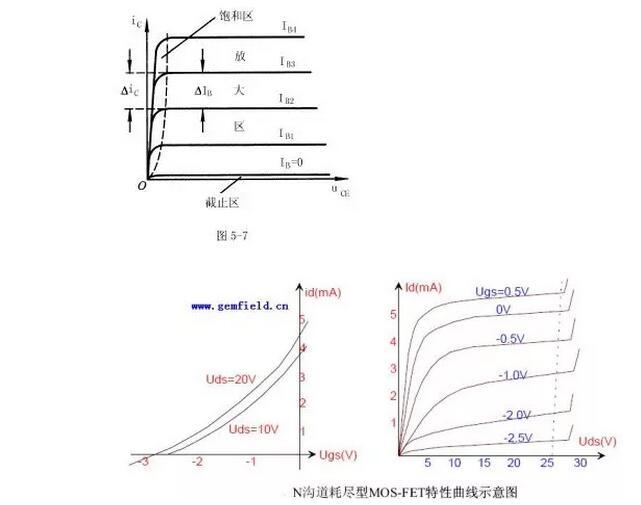

关于晶体三极管的开关饱和区,MOS管的饱和区就是晶体管的放大区。

晶体三极管的放大是电流关系的放大,即Ic=B*Ib

而MOS管的放大倍数是Ic=B*Ugs,与g、s两端的电压有关系

MOS管的放大倍数比较大,稳定。

2.基极电阻的选取

(1)首先判断三极管的工作状态,是放大区(增大驱动电流)还是饱和区(开关作用)

(2)若工作在放大区,根据集电极负载的参数,计算出集电极的电流,之后根据三级管的放大特性计算出基极电流,再根据电流值计算出电阻。

(3)若工作在饱和区,

以NPN管为例大致计算一下典型3元件开关电路的选值:

设晶体管的直流放大系数为100,Ib=(驱动电压-0.7Vbe结压降)/Rb,Vce=Vcc-100Ib×Rc,令Vce=0,由此可算出临界值(饱和区与放大区的临界),只要Rb小于临界值即可,但其最小值受器件Ib容限限制,切勿超过。

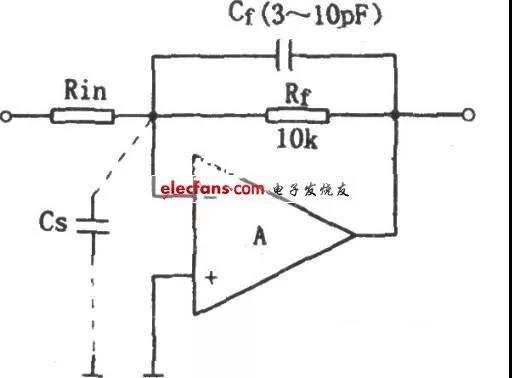

3.补偿电容电路图

一般线性工作的放大器(即引入负反馈的放大电路)的输入寄生电容Cs会影响电路的稳定性,其补偿措施见图。放大器的输入端一般存在约几皮法的寄生电容Cs,其频带的上限频率约为:

ωh=1/(2πRfCs)

为了保持放大电路的电压放大倍数较高,更通用的方法是在Rf上并接一个补偿电容Cf,使RinCf网络与RfCs网络构成相位补偿。RinCf将引起输出电压相位超前,由于不能准确知道Cs的值,所以相位超前量与滞后量不可能得到完全补偿,一般是采用可变电容Cf,用实验和调整Cf的方法使附加相移最小。若Rf=10kΩ,Cf的典型值丝边3~10pF。对于电压跟随器而言,其Cf值可以稍大一些。

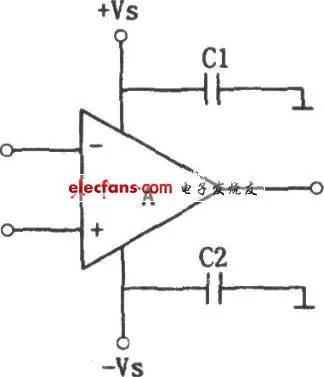

4.运放电源旁路电容

旁路是把前级或电源携带的高频杂波或信号滤除,去藕是为保证输出端的稳定输出

每个集成运放的电源引线,一般都应采用去偶旁路措施,如图所示图中的高频旁路电容,通常可选用高频性能优良的陶瓷电容,其值约为0.1μF。或采用lμF的钽电容。这些电容的内电感值都较小。在运放的高速应用时,旁路电容C1和C2应接到集成运放的电源引脚上,引线尽量短,这样可以形成低电感接地回路。

注:当所使用的放大器的增益带宽乘积大于10MHz时,应采用更严格的高频旁路措施,此时应选用射频旁路电容,对于通用集成芯片,对旁路的要求不高,但也不能忽视,通常最好每4~5个器件加一套旁路电容。不论所用集成电路器件有多少,每个印刷板都要至少加一套旁路电容。

在直流电源回路中,负载的变化会引起电源噪声。例如在数字电路中,当电路从一个状态转换为另一种状态时,就会在电源线上产生一个很大的尖峰电流,形成瞬变的噪声电压。配置去耦电容可以抑制因负载变化而产生的噪声,是印制电路板的可靠性设计的一种常规做法,配置原则如下:

●电源输入端跨接一个10~100uF的电解电容器,如果印制电路板的位置允许,采用100uF以上的电解电容器的抗干扰效果会更好。

●为每个集成电路芯片配置一个0.01uF的陶瓷电容器。如遇到印制电路板空间小而装不下时,可每4~10个芯片配置一个1~10uF钽电解电容器,这种器件的高频阻抗特别小,在500kHz~20MHz范围内阻抗小于1Ω,而且漏电流很小(0.5uA以下)。

●对于噪声能力弱、关断时电流变化大的器件和ROM、RAM等存储型器件,应在芯片的电源线(Vcc)和地线(GND)间直接接入去耦电容。

●去耦电容的引线不能过长,特别是高频旁路电容不能带引线。

在直流电源回路中,负载的变化会引起电源噪声。例如在数字电路中,当电路从一个状态转换为另一种状态时,就会在电源线上产生一个很大的尖峰电流,形成瞬变的噪声电压。配置去耦电容可以抑制因负载变化而产生的噪声,是印制电路板的可靠性设计的一种常规做法,配置原则如下:

●电源输入端跨接一个10~100uF的电解电容器,如果印制电路板的位置允许,采用100uF以上的电解电容器的抗干扰效果会更好。

●为每个集成电路芯片配置一个0.01uF的陶瓷电容器。如遇到印制电路板空间小而装不下时,可每4~10个芯片配置一个1~10uF钽电解电容器,这种器件的高频阻抗特别小,在500kHz~20MHz范围内阻抗小于1Ω,而且漏电流很小(0.5uA以下)。

●对于噪声能力弱、关断时电流变化大的器件和ROM、RAM等存储型器件,应在芯片的电源线(Vcc)和地线(GND)间直接接入去耦电容。

●去耦电容的引线不能过长,特别是高频旁路电容不能带引线。在直流电源回路中,负载的变化会引起电源噪声。例如在数字电路中,当电路从一个状态转换为另一种状态时,就会在电源线上产生一个很大的尖峰电流,形成瞬变的噪声电压。配置去耦电容可以抑制因负载变化而产生的噪声,是印制电路板的可靠性设计的一种常规做法,配置原则如下:

●电源输入端跨接一个10~100uF的电解电容器,如果印制电路板的位置允许,采用100uF以上的电解电容器的抗干扰效果会更好。

●为每个集成电路芯片配置一个0.01uF的陶瓷电容器。如遇到印制电路板空间小而装不下时,可每4~10个芯片配置一个1~10uF钽电解电容器,这种器件的高频阻抗特别小,在500kHz~20MHz范围内阻抗小于1Ω,而且漏电流很小(0.5uA以下)。

●对于噪声能力弱、关断时电流变化大的器件和ROM、RAM等存储型器件,应在芯片的电源线(Vcc)和地线(GND)间直接接入去耦电容。

●去耦电容的引线不能过长,特别是高频旁路电容不能带引线。

转自:

https://www.cnblogs.com/jacklong-yin/articles/8862129.html