设计目标:

•电源电压: 5 V

•输入电压: 0 V – 2 V

•输出电流: 0 mA – 100 mA

电路原理

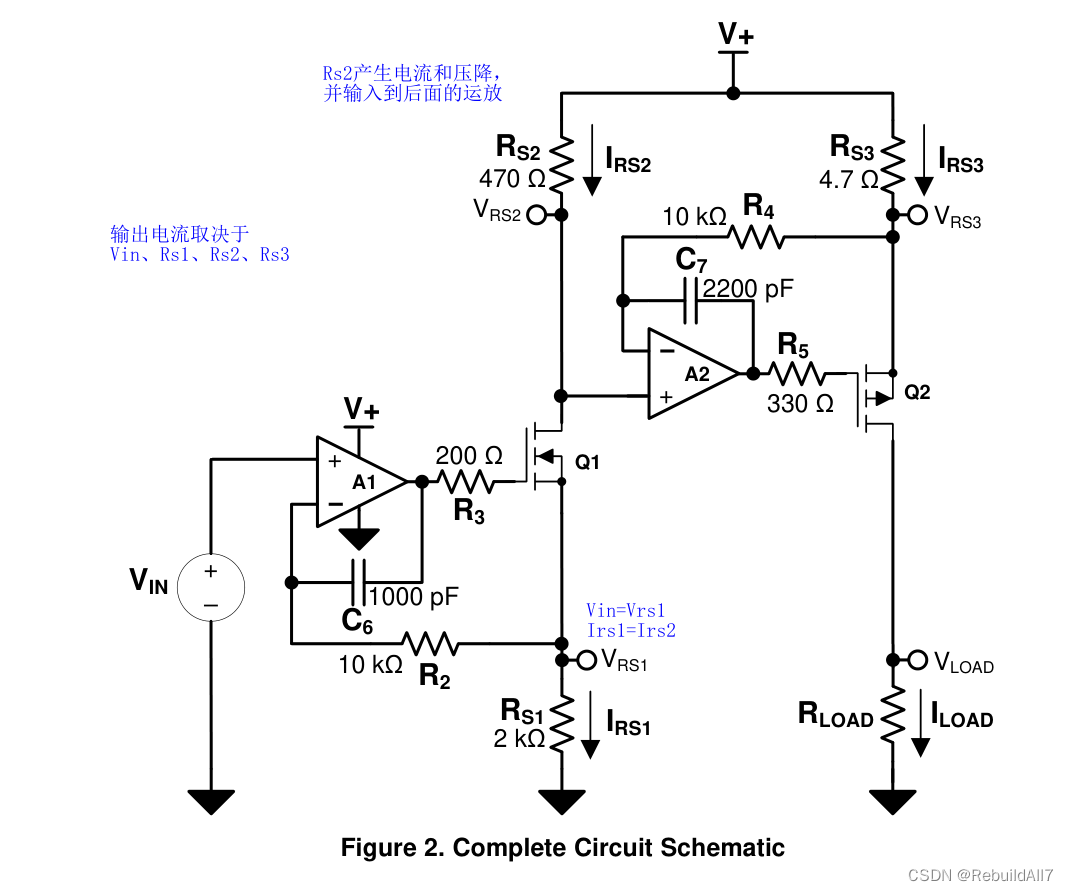

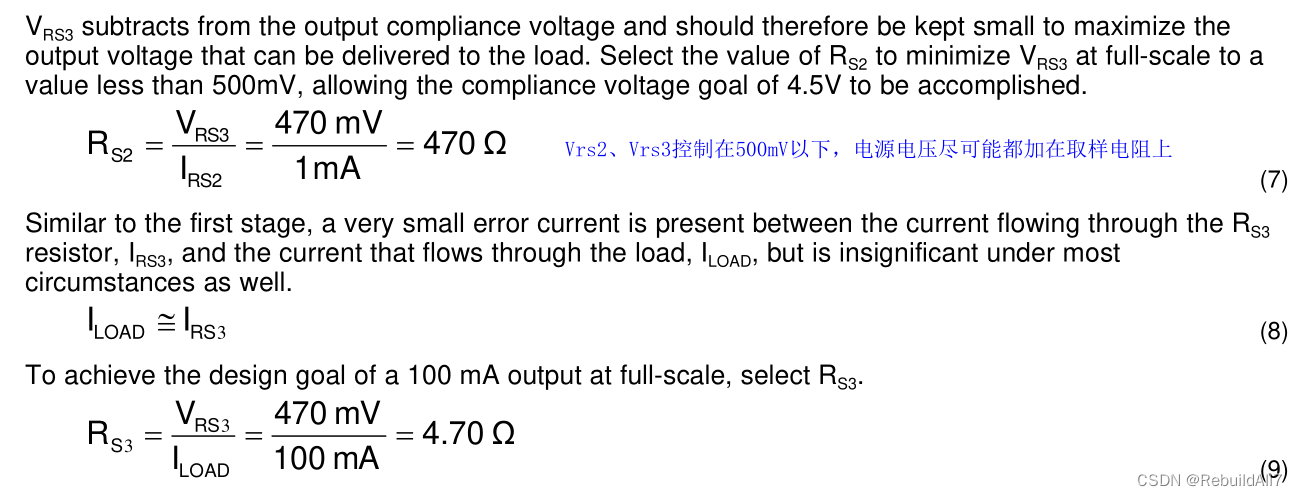

电路组成分为两级:

第一级使用运放和NMOS,将以地为基准的输入(电压)转换为以电源为基准的信号。该信号通过运放来控制PMOS,从而调节负载电流。第一级叫电流吸收Current Sink,第二级叫电流源

Current Source。

V-I关系取决于输入电压Vin和三个电流感应电阻Rs1, Rs2,和 Rs3;

输入电压Vin与电阻Rs1决定了第一级电路的电流,Rs2,和 Rs3决定了第一级到第二级的电流增益

1、Current Sink

流经Rs2的电流产生一个压降,用于驱动下一级电路。根据“虚短虚断”,Rs1电压等于Vin,由于我们的设计目标是0-2V输入,因此:

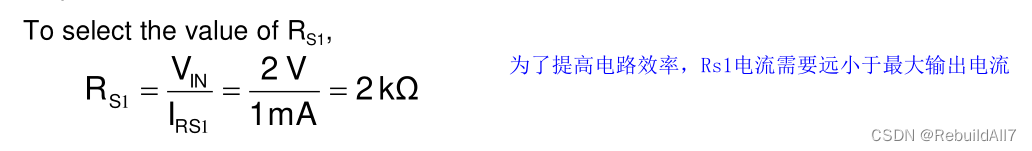

电路的第一级不向负载输送功率,因此第一级中由电源产生的电流等于是损耗了,降低了电路的能量转换效率。另外,运放的静态电流也会消耗能量。为了减少第一级的能量损耗,我们将第一级的电流设计为最大1mA,即整个电路满量程电压输入2V电流输出100mA时,电阻Rs1上面流过1mA 。因此,改电阻选型就出来了:

NMOS管导通后,上下电流相等(导通条件是什么????)

2、 Current Source

第二级输出的电流,可以驱动负载,第二级运放的同向输入端取自电阻Rs2上面的压降,根据“虚短虚断”:

为了将电源电压都加在负载电阻上面,Rs3需要尽可能的小。满量程时:

3、补偿组件

第一级和第二级都需要补偿部件以确保适当的设计稳定性。第一级的 R2, R3, C6、第二级的R4, R5, C7都是用于补偿电路的。

一、运放输出端连接MOS管的电阻是隔离电阻:将运放 与MOS管栅极的容性负载(寄生电容)隔离;

二、MOSFET的增益 在高频下通过运算放大器输出端直接提供反馈到运放的反相输入端的反馈电容 在反馈回路中去除,这种转变发生的频率大致基于由CF和RF值形成的RC时间常数。

补偿元件的选项和取值不是一成不变的,需要不断实验改进。

这两个电阻和一个电容,先从比较小的取值开始,比如:10 Ω for RISO, 10 kΩ for RF, and 100 pF for CF

如果不使用所有三个组件,电路将不稳定,接下来的步骤也将无法工作。

方法与步骤:对电路的输入施加小信号阶跃响应,并观察运算放大器的输出和负载电流。开始增加运算放大器输出和MOSFET栅极之间的串联电阻值,直到获得几乎没有振铃和过冲的响应。然后开始增加反馈电容的值,直到达到最终期望的响应。如果在过冲、振铃或振荡得到解决之前,响应过度抑制,则进一步增加串联电阻,并重新开始电容器尺寸确定过程。可先使用SPICE TINA-TI仿真。

器件选型

1、运放

低偏移电压、低温度漂移和轨对轨输出。low offset voltage, low temperature drift, and rail-to-rail output.

本例选择OPA2333

轨对轨输出运算放大器的输出摆幅,能够完全控制供电轨内的MOSFET器件的栅极。

2、MOS管

不能超过电气参数,确定最大的Vgs(gate-to-source voltage),drain-to-source voltage (Vds),drain current (ID), (Vgs(th))要小,便于运放控制,本电路选择的SI2304DS n-channel MOSFET and NTF2955 p-channel MOSFET(选择大电流大封装,避免发热)

3、无源器件

电阻选择0.1%精度,温漂低,尤其是Rs1 Rs2 Rs3

仿真图纸

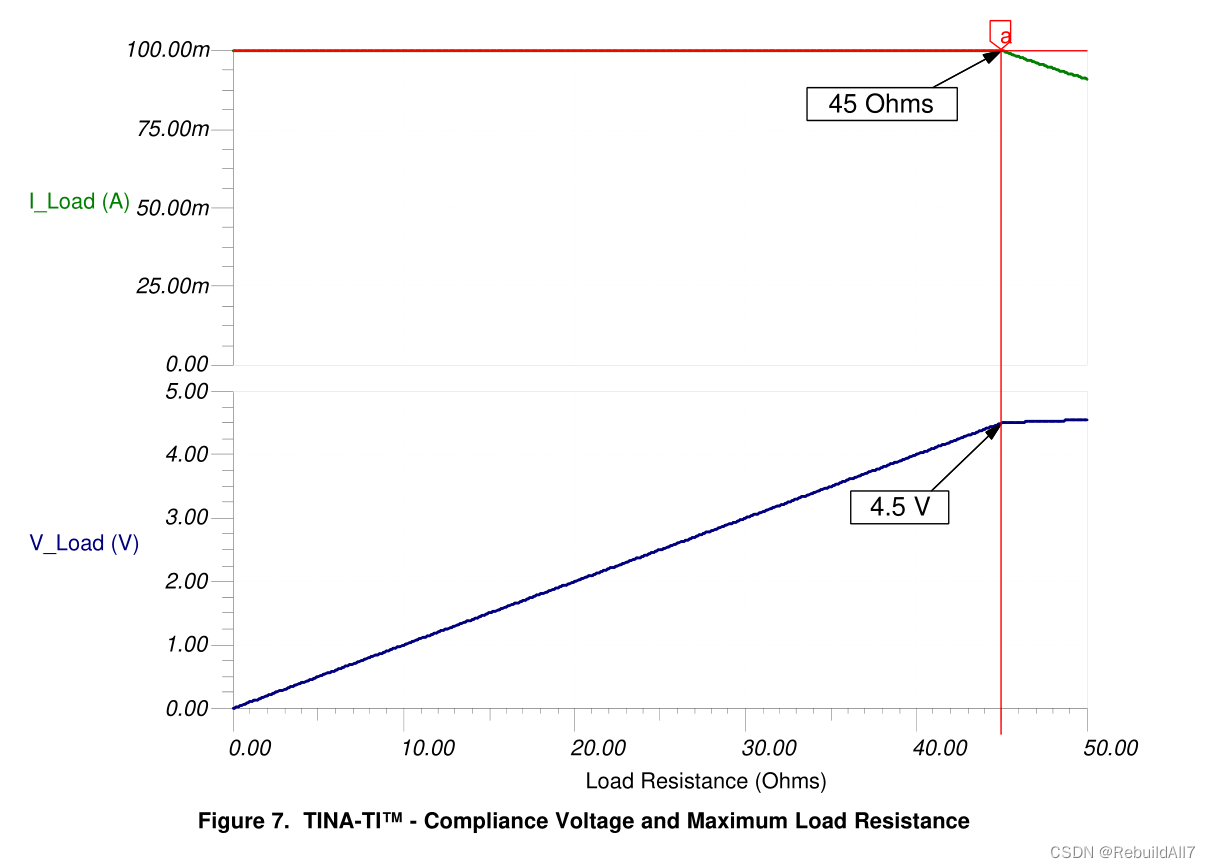

带载能力

PCB设计

PCB走线电阻会影响本设计的精度,尤其是电流输出值比较大的时候,寄生电阻会带来更大的误差

所有3个电流取样电阻到运放都具有Kelvin连接,Kelvin连接,也称为四端传感,将传感信号与电源信号分离,从而消除PCB迹线阻抗导致的电压降。

RS2 RS3紧挨在一起,确保电压电势相等

替代型号

电流环的带载能力取决于电源电压,电压越高带载越大

当修改设计以获得更高的电压或更大的输出电流时,应注意确保设计中的MOSFET和其他部件不会过超过最大电气参数。

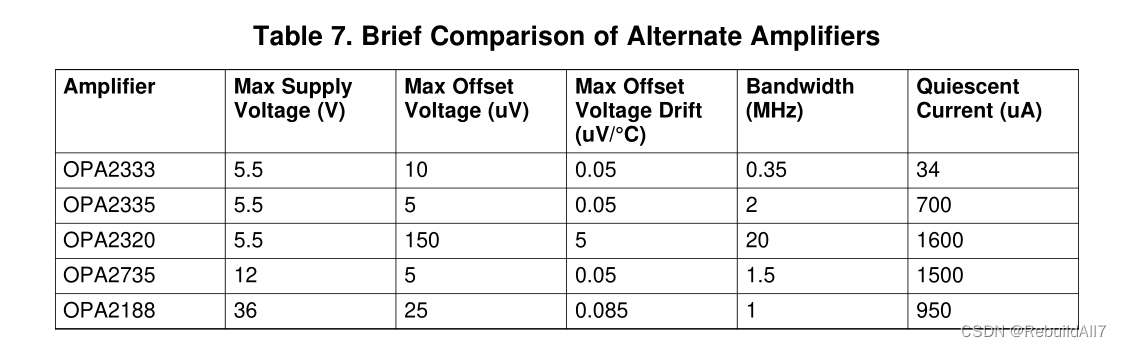

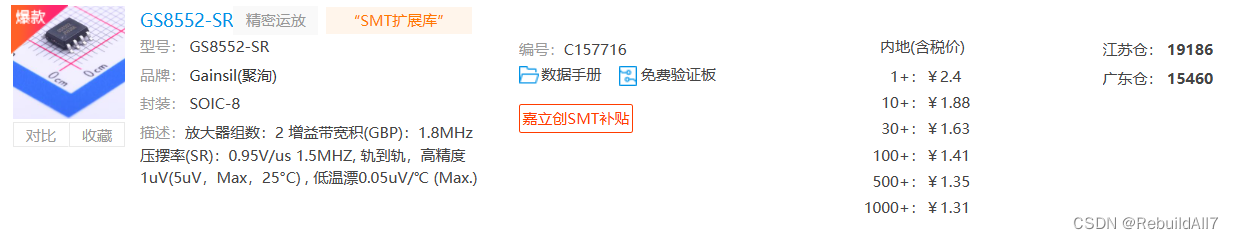

精密运放OPA2333替代型号

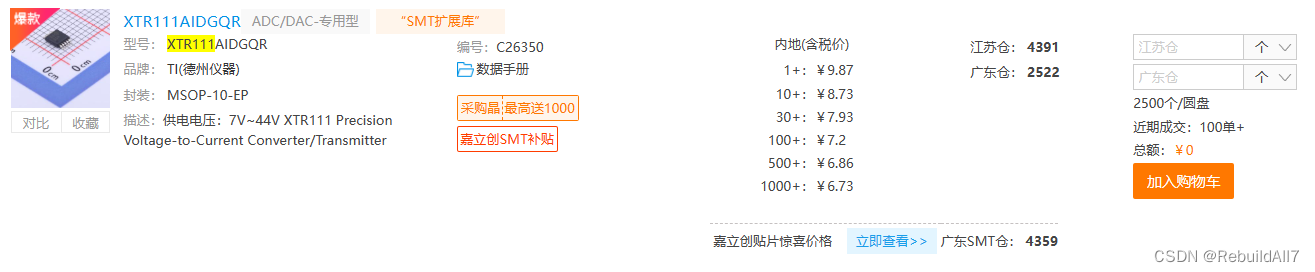

XTR110(无货)和XTR111,集成了本设计中所示的电路,以创建常见的工业电流回路输出,如4–20 mA和其他类似范围。这些设备还具有电压调节器、错误标志和其他功能,有助于创建强大的电流回路输出模块。

2023年3月25日价格

转自:https://blog.csdn.net/CSDN_XIAXIA/article/details/128956415