1 Arm architecture

Arm 架构是世界上最流行的处理器架构之一。每年有数十亿台基于 Arm 的设备出货。

|

A-Profile (Applications) |

R-Profile (Real-Time) |

M-Profile (Microcontroller) |

|---|---|---|

|

高性能场景 |

实时系统 |

小型,高能效设备 |

|

用于运行复杂的操作系统,如Linux,Windows |

网络和嵌入式设备 |

物联网设备 |

Arm Cortex 和 Arm Neoverse 是用于 Arm 处理器 IP 产品的品牌名称。

下图显示了基于 Arm 的系统示例:

此示例智能手机包含以下处理器类型:

-

A-profile 处理器作为主要 CPU 运行像 Android 这样的 rich OS。

-

基于 R-profile 处理器的蜂窝调制解调器提供连接性。

-

多种 M-profile 处理器如:系统电源管理。

-

SIM 卡使用 SecurCore,这是一种具有附加安全功能的 M-profile 处理器。SecurCore 处理器通常用于智能卡。

在本指南中,我们将只介绍 A-profile 架构及其两个最新版本 Armv8-A 和 Armv9-A。

1.1 架构是什么?

当我们使用术语架构时,我们指的是功能规范。在 Arm 架构下,我们指的是处理器的功能规范。架构指定了处理器的行为方式,例如它有什么指令以及指令做什么。

可以将架构视为硬件和软件之间的契约。架构描述了软件可以依赖硬件来提供哪些功能。正如我们在架构和微架构中解释的那样,一些功能是可选的。

Arm架构规定:

|

– |

说明 |

|---|---|

|

指令集 |

每条指令的功能 指令在内存中如何存储(编码方式) |

|

寄存器 |

有多少寄存器 寄存器有多少位 寄存器的功能 寄存器初始态 |

|

异常模型 Exception model |

不同等级的权限 不同异常的类型 发生条件和返回条件 |

|

存储模型 Memory model |

什么内存可以乱序 cache的行为,软件如何管理 |

|

Debug trace |

如何设置并触发断点 trace工具能获得什么信息 |

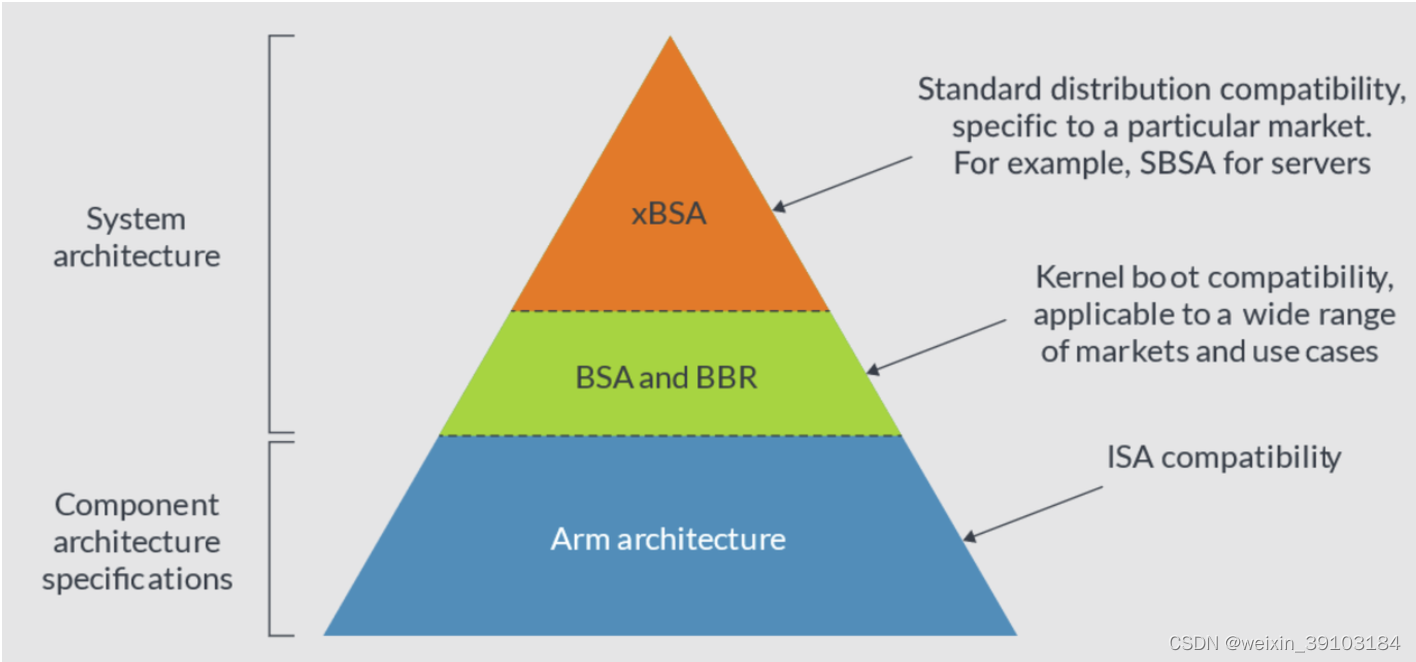

1.2. 系统架构

系统不仅仅包括一个处理器内核。Arm 还提供了规范来描述包含处理器的系统的要求,如下图所示:

规范是软件兼容性的基础。按照规范构建硬件意味着可以编写与之匹配的软件。按照规范编写软件意味着它可以在兼容的硬件上运行。Arm 架构是第一层,通过指令集(ISA,Instruction Set Architecture )兼容性向软件提供通用的程序员模型。

基础系统架构(BSA,Base System Architecture)规范描述了系统软件可以依赖的硬件系统架构。BSA 涵盖了处理器和系统架构的各个方面,例如中断控制器、定时器和 OS 需要的其他常见设备。这为标准操作系统、hypervisors 和固件提供了一个可靠的平台。

BSA 广泛适用于不同的市场和用例。其他标准可以建立在 BSA 的基础上,以提供特定市场的标准化。例如,服务器基础系统架构(SBSA,Server Base System Architecture)是针对服务器的 BSA 的补充。SBSA 描述了服务器 OS 的硬件和功能要求。该规范包含一组级别,随着 CPU 架构的发展,这些级别越来越详细地记录硬件功能。

基本引导要求(BBR,Base Boot Requirements)规范涵盖了基于 Arm 体系结构以及操作系统和虚拟机监控程序可以依赖的系统的要求。该规范确立了固件接口要求,如 PSCI、SMCCC、UEFI、ACPI 和 SMBIOS。

BBR 还提供了针对特定用例的场景,例如:

-

SBBR:指定 UEFI、ACPI 和 SMBIOS 要求来启动通用的、现成的操作系统和管理程序,如Windows, VMware, RHEL, Oracle Linux, Amazon Linux。SBBR 还支持其他操作系统,如 Debian、Fedora、CentOS、SLES、Ubuntu、openSUSE、FreeBSD 和 NetBSD。

-

EBBR:与 EBBR 规范一起,指定 UEFI 要求以启动通用的现成操作系统,如 Debian、Fedora、Ubuntu、openSUSE,并为垂直集成的 OS 平台提供优势。

-

LBBR:指定 LinuxBoot 固件的潜在要求,以引导某些超大规模程序使用的操作系统。

1.3. 架构和微架构

架构不会告诉你处理器是如何构建或是如何工作的。处理器的构建和设计称为微架构。微架构告诉你特定处理器的工作原理。

-

流水线长度和分配

-

cache数量和大小

-

每条指令执行周期数

-

未实现的功能

-

实现的可选功能

例如,Cortex-A53 和 Cortex-A72 都是 Armv8-A 架构的实现。这意味着它们具有相同的架构,但它们具有非常不同的微架构,如下图和表格所示:

|

Architecture |

Cortex-A53 |

Cortex-A72 |

|---|---|---|

|

Target |

优化能效比 |

优化性能 |

|

Pipeline |

8 级流水 顺序执行 |

15+ 流水 乱序执行 |

|

Caches |

L1 I cache: 8KB – 64KB L1 D cache: 8KB – 64KB L2 cache: optional, up to 2MB |

L1 I cache: 48KB fixed L1 D cache: 32KB fixed L2 cache: mandatory, up to 2MB |

架构兼容的软件无需修改即可在 Cortex-A53 或 Cortex-A72 上运行。这是因为它们都实现了相同的架构。

1.4. Arm 架构发展

Arm 架构随着时间的推移而发展,每个版本都建立在之前的基础上。

通常会看到被称为以下内容的架构:Armv8-A:这意味着架构版本是8,A-Profile。或者,简而言之:v8-A

- Armv8-A:Armv8-A 于 2011 年发布,是 Arm 架构的第一个 64 位版本。基于 Armv8-A 的设备已部署在从手机到超级计算机的所有领域。

- Armv9-A:Armv9-A 是 Arm Architecture for A-profile 的最新版本。Armv9-A 建立在 Armv8-A 之上并添加了新功能,包括:

-

Scalable Vector Extension, version 2 (SVE2)

-

Transactional Memory Extension (TME)

-

Branch Record Buffer Extension (BRBE)

-

Embedded Trace Extension (ETE)

-

Trace Buffer Extension (TRBE)

-

此外,Armv8-A 中的一些可选功能在 Armv9-A 中是必须的。

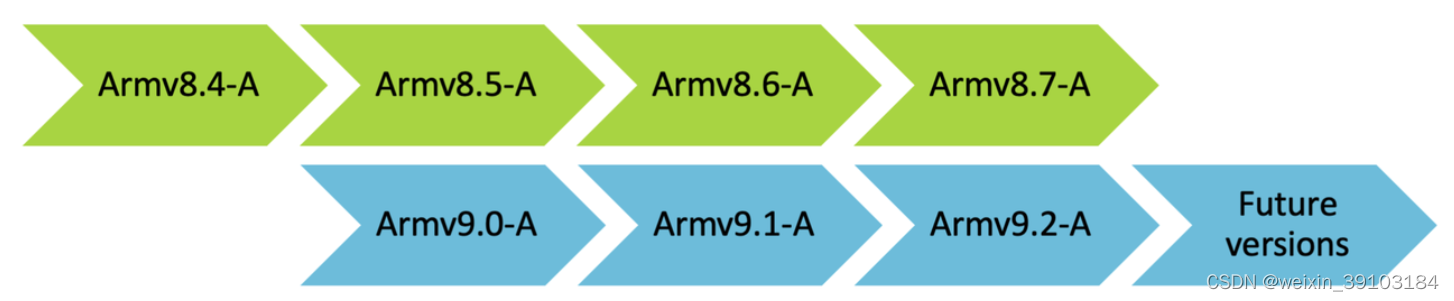

Arm 发布架构年度更新,增加新的指令和功能。Armv9.0-A 与 Armv8.5-A 对齐,继承 Armv8.5-A 的所有功能并增加新功能。Armv9-A 初始发布后,Armv8-A 和 Armv9-A 一起更新。Arm 将发布 Armv9-A 的新功能,并将继续更新和维护 Armv8-A。下图显示了并行版本:

您可以在Understanding the Armv8.x extensions.中找到有关每个年度更新中添加的内容的更多信息。

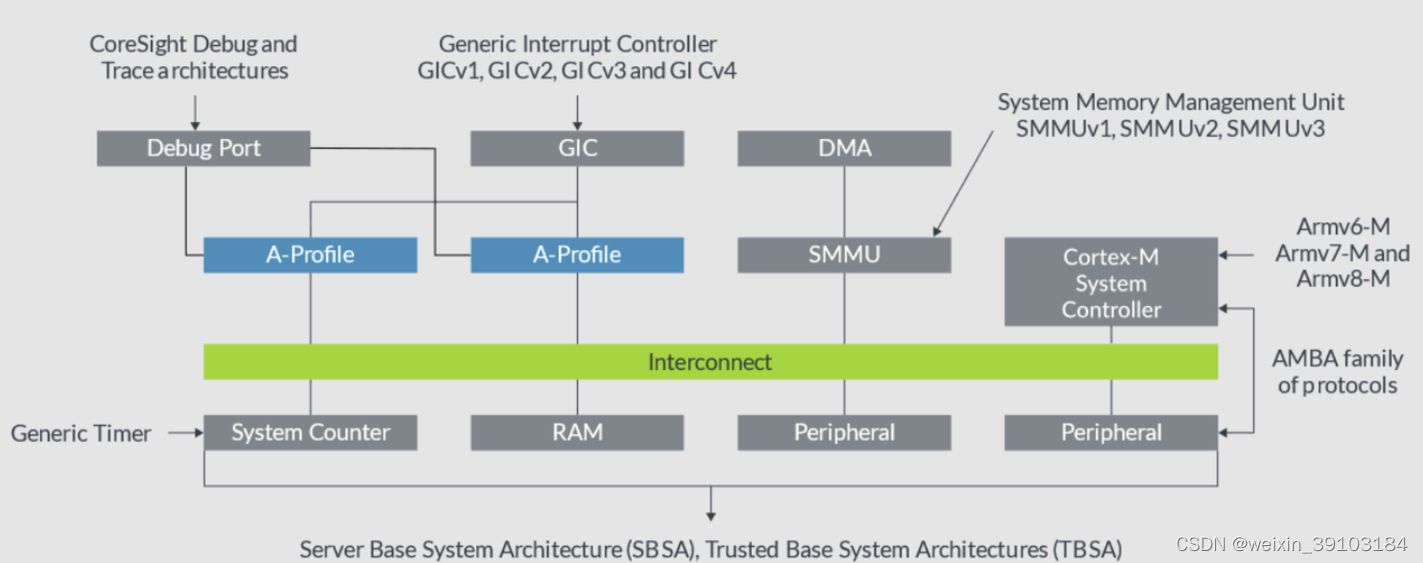

1.5. 其他 Arm 架构

Arm 架构是最著名的 Arm 规范,但它不是唯一的。Arm 对构成现 SoC 的许多组件具有类似的规范。下图提供了一些示例:

-

通用中断控制器:通用中断控制器(GIC)规范是用于 Armv7-A/R 和 Armv8-A/R 的标准化中断控制器。

-

系统内存管理单元:系统内存管理单元(SMMU 或有时是 IOMMU)为非处理器主机提供翻译服务。

-

通用定时器:通用定时器为系统中的所有处理器提供一个通用的参考系统计数。这些定时器提供用于操作系统调度器时钟等功能。通用定时器是 Arm 架构的一部分,但系统计数器是系统组件。

-

服务器基础系统架构和可信基础系统架构:服务器基础系统架构(SBSA)和可信基础系统架构(TBSA)为 SoC开发人员提供系统设计指南。

-

高级微控制器总线架构:高级微控制器总线架构(AMBA, Advanced Microcontroller Bus Architectur)系列总线协议控制基于 Arm 的系统中组件的连接方式以及这些连接上的协议。

1.6. 了解 Arm 文档

Arm 为开发人员提供了很多文档。在指南的这一部分中,我们将解释在哪里可以找到文档和其他信息,以便在 Arm 上进行开发。

文档在哪里?

你可以从 Arm 开发者网站下载Arm架构和处理器手册。

您可以向 Arm 社区的 Arm 专家提出开发问题并查找有关特定主题的文章和博客。

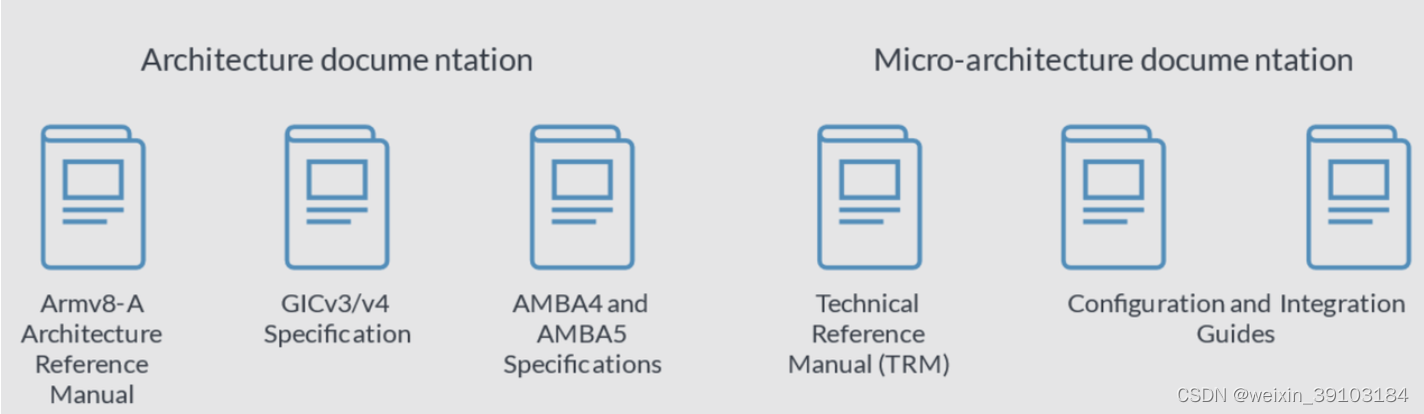

每个文件描述了什么?

以下是对不同类型文档的简要说明:

-

每个 Arm 架构参考手册(Arm Architecture Reference Manual)都描述了一个架构规范。Arm 架构参考手册与该架构的任何实现相关。

-

每个 Arm Cortex 处理器都有一个技术参考手册(TRM,Technical Reference Manual)。TRM 描述了特定于该处理器的功能。一般来说,TRM 不会重复 Arm 架构参考手册中给出的任何信息。

-

每个 Arm Cortex 处理器还有一个配置和集成手册(CIM,Configuration and Integration Manual),CIM 描述了如何将处理器集成到系统中,通常,这些信息仅与 SoC 设计人员相关。

CIM 仅适用于 IP 被许可人。TRM 无需许可即可从 Arm Developer 下载

对我来说意味着什么?

如果你正在查找有关特定处理器的信息,您可能需要参考几个不同的文档。在这里,我们可以看到您可能需要与 Cortex-A75 处理器一起使用的不同文档:

Cortex-A75 实现了 ARMv8.2-A、GICv4 CPU 接口和 AMBA 总线接口,因此您必须参考每个部分的单独文档。您还必须参考描述微架构的文档。

如果您正在使用现有的 SoC,您还将使用 SoC 制造商的留档。此文档通常称为数据表。数据表提供特定于该 SoC 的信息。

下表显示了不同类型文档中显示的信息:

|

– |

Architecture |

– |

– |

Micro-architecture |

Micro-architecture |

– |

|---|---|---|---|---|---|---|

|

Arm Architecture Reference Manual |

GIC specifications |

AMBA specifications |

TRM |

CIM |

SoC Datasheet |

|

|

Instruction set |

x |

|||||

|

Instruction cycle timings |

x |

|||||

|

Architectural registers |

x |

x |

||||

|

Processor specific registers |

x |

|||||

|

Memory model |

x |

|||||

|

Exception model |

x |

|||||

|

Support for optional features |

x |

x (some might be synthesis choice) |

||||

|

Size of caches/TLBs |

x |

|||||

|

Power management |

x |

|||||

|

Bus ports |

x |

x |

||||

|

All legal bus transactions |

x |

|||||

|

Bus transactions generated by processor |

x |

|||||

|

Memory map |

x |

|||||

|

Peripherals |

x |

|||||

|

Pin-out of SoC |

x |

参考手册和用户指南之间的差异

目前我们看过的文档,Arm 架构参考手册、TRM 和 CIM 都是参考手册。这意味着它们没有提供如何使用处理器的指导。例如,Arm 架构参考手册没有关于如何打开 MMU 的部分。

这种结构是经过深思熟虑的,目的是在架构要求的技术细节(可在参考手册中找到)和提供更一般指导的文档(例如本指南)之间保持明确的划分。一些一般指导文档将介绍概念,而另一些则提供说明供您遵循。

1.7. 常见架构术语

架构使用了几个术语,通常用留档中的小写大写字母书写,它们具有非常具体的含义。Arm 架构参考手册定义了这些术语中的每一个。在本节中,我们将查看最常见的术语,并提供有关它们对程序员意味着什么的附加信息。

PE

处理元素(PE,Processing Element)是 Arm 架构实现的通用术语。您可以将 PE 视为任何具有自己的程序计数器并可以执行程序的东西。例如,Arm 架构参考手册指出:

确定 PE 如何运行的状态,包括当前的异常级别和安全状态,以及在 AArch32 状态下的 PE 模式。

手册使用通用术语 PE,因为有许多不同的潜在微架构。例如,在 Arm Cortex-A 处理器中可以使用以下微架构:

-

Cortex-A8 是一个单核、单线程处理器。整个处理器是一个 PE。

-

Cortex-A53 是一个多核处理器,每个内核都是一个单线程。每个内核都是一个 PE。

-

Cortex-A65AE 是一个多核处理器,每个内核有两个线程。每个线程都是一个 PE。

通过使用术语 PE,架构与在不同处理器中做出的特定设计决策保持分离。

IMPLEMENTATION DEFINED

IMPLEMENTATION DEFINED(简称 IMP DEF)的特性由特定的微架构定义。实现必须呈现一致的行为或值。

例如,缓存的大小是 IMP DEF。该架构为软件提供了一种定义的机制来查询缓存大小,但缓存的大小取决于处理器设计人员。

同样,对密码学指令的支持是 IMP DEF。同样,有寄存器允许软件确定指令是否存在。

在这两个示例中,选择都是静态的。也就是说,给定的处理器要么支持,要么不支持功能和指令。功能的存在在运行时不能改变。

对于 Cortex-A 处理器,一些 IMP DEF 选项将是固定的,一些将是合成选项。例如,在 Cortex-A57 上,L1 缓存的大小是固定的,L2缓存的大小是合成选项。但是,关于 L2 缓存大小的决定是在设计时做出的。它在运行时仍然是静态的。

IMP DEF 选项的全部详细信息记录在特定处理器的技术参考手册(TRM)中。

UNPREDICTABLE 和 CONSTRAINED UNPREDICTABLE

UNPREDICTABLE 和 CONSTRAINED UNPREDICTABLE 用于描述软件不应该做的事情。

当某些事情不可预测或受限不可预测时,软件不能依赖处理器的行为。如果软件多次执行不良操作,处理器也可能表现出不同的行为。

例如,提供未对齐的翻译表是 CONSTRAINED UNPREDICTABLE。这代表坏软件。坏软件是违反翻译表应遵守的架构规则的软件。

与 IMP DEF 行为不同,技术参考手册(TRM)通常不会描述所有不可预测的行为。

Deprecated

有时,我们会从架构中删除某个功能。可能会有几种原因,例如性能或因为该功能不再常用,没有必要。但是,仍然可能有一些遗留软件依赖该功能。因此,在完全删除某个功能之前,我们首先将其标记为已弃用。例如,Arm 架构参考手册指出:

出于性能原因,不建议使用 IT 指令以及 CP15DMB、CP15DSB 和 CP151SB 屏障指令。

DEPRECATED 是对开发人员的警告,即将来将删除某个功能,并且他们应该开始从代码中删除它。

通常,一个控件会同时添加到架构中,允许禁用该功能。此控件允许开发人员测试该功能在遗留代码中的使用。

RES0 和 RES1

RES0 表示保留,应该为零。RES1 表示保留,应该为一。

RES0 和 RES1 用于描述未使用且对处理器没有功能影响的字段。

保留字段可能会在架构的某个未来版本中使用。在这种情况下,RES0/RES1 字段值 1 将提供新行为。

RES0 字段不会始终读取为 0,RES1 字段可能不会始终读取为 1。RES0 和 RES1 只告诉您该字段未使用。

有时 RES0 和 RES1 字段必须是有状态的。有状态意味着字段读回最后写入的值。

1.8. QA

如果在文档中看到了 Armv7-R,那么指的是架构的哪个版本?

版本 7,R-Profile

在哪个版本的 Arm 架构中添加了 64 位支持到 A-Profile 中?

版本8(Armv8-A)

对于以下每一项,您会将它们归类为架构还是微架构:指令编码、缓存大小和内存排序?

指令编码:架构

缓存大小:微架构

内存排序:架构

什么是 PE?

PE 是一种处理元件:实现 Arm 架构的机器。

转自:

https://blog.csdn.net/weixin_39103184/article/details/130470763