序言

电子钟亦称数显钟(数字显示钟),是一种用数字电路技术实现时分、秒

计时的装置,与机械时钟相比,直观性为其主要显著特点,且因非机械动,

具有更长的使用寿命,相较石英钟的石英机芯驱动,更具准确性。

电子钟是一个将“时”,“分”,“秒”显示于人的视觉器官的计时装置。它的时

周期为 24 小时,显示满刻度为 23 时 59 分 59 秒,具有校时功能和报时功能

因此,一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器、校

时电路、报时电路和振荡器组成。

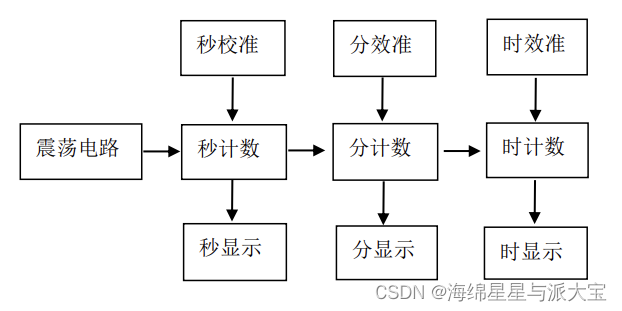

主电路系统由秒信号发生器、“时、分、秒”计数器、译码器及显示器、校

时电路、整点报时电路组成。秒信号的产生利用 NE555 制成的多谐震荡器产

生脉冲。将标准秒信号送入“秒计数器”,“秒计数器”采用 60 进制计数器,每累

计 60 秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计

数器”也采用 60 进制计数器,每累计 60 分钟,发出一个“时脉冲”信号,该信

号将被送到“时计数器”。“时计数器”采用 24 进制计时器,可实现对一天 24 小

时的累计。译码显示电路将“时”、“分”、“秒”计数器的输出状态用七段显示译

码器译码,最后通过七段数码管显示出来。整点报时电路时根据计时系统的

输出状态产生脉冲信号,然后去触发蜂鸣器实现报时。

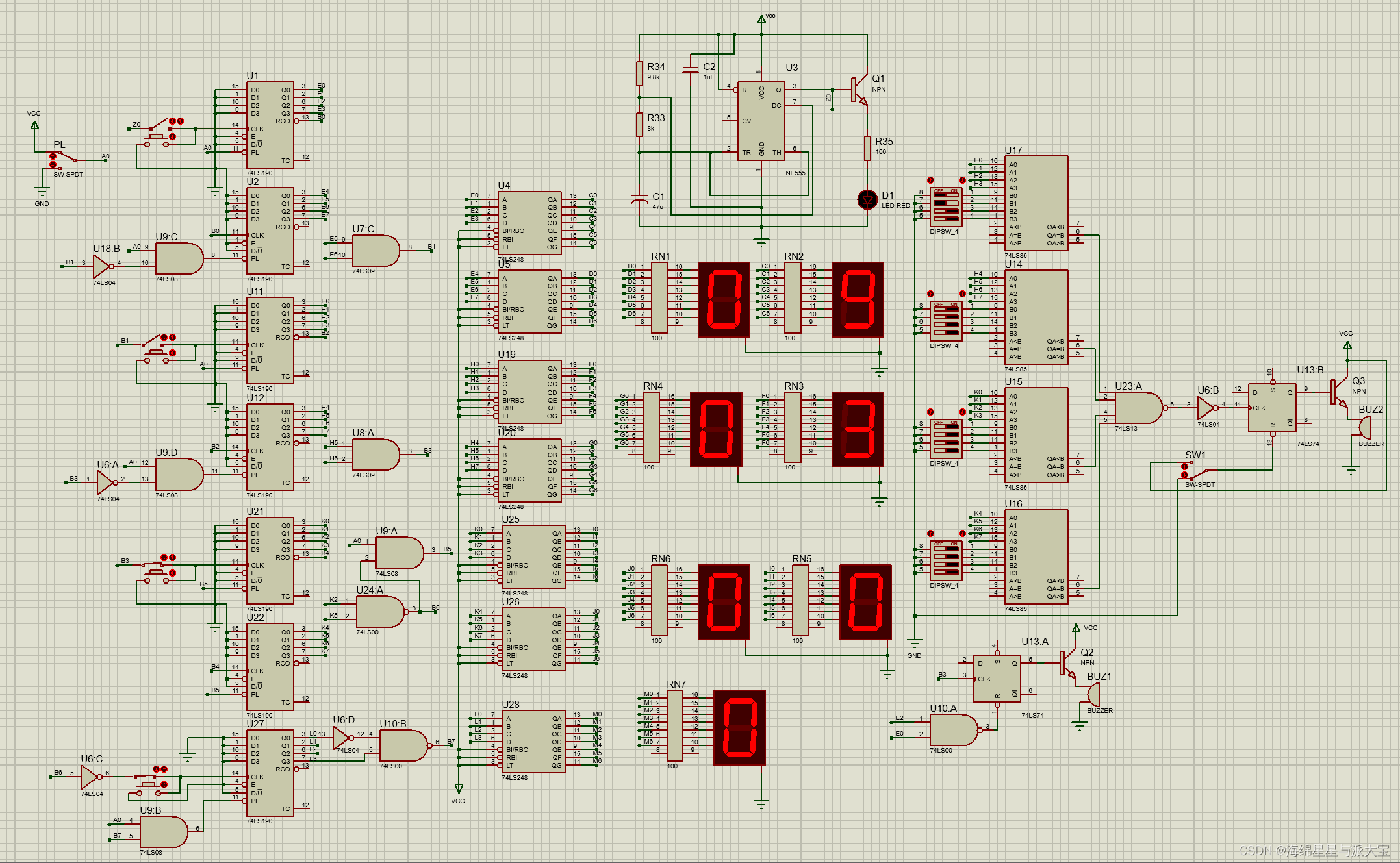

完成仿真电路图

(图片用手机看可能不清晰,建议用电脑查看)

1、设计目的

(1)掌握数字时钟的设计方法

(2)掌握简单数字电路系统的设计方法,培养设计数字电路系统的能力

(3)提高对计数、译码、显示、调试等数字电路系统运用的能力

2、设计要求

利用基本的数字电路制作小时电子钟,要求显示时分秒;并能实现校时

和校分的功能。

3、功能拓展

(1)针对影响电子钟走时精度的因素提出改进方案

(2)增加日期显示

(3)实现倒计时功能

(4)整点报时

(5)定时功能

4、所用元件

计数器(74LS190)——7 个 显示译码器(74LS248)——6 个

D 触发器——2 个 数码显示管——6 个

开关 ——若干个 与门——8 个

与非门——3 个 非门——5 个

四位开关——4 个 蜂鸣器——2 个

三级管(NPN)——3 个 电容、电阻——若干个

NE555——1 个 二极管——1 个

5、实验原理

(1)思维导图

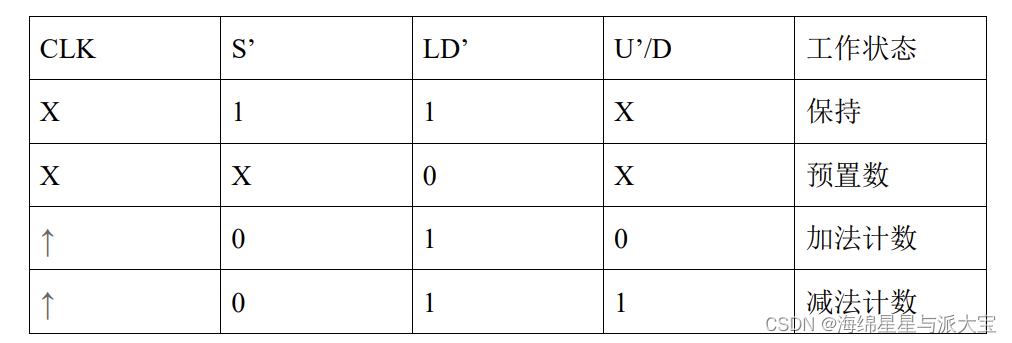

(2)计数器 74LS190 的功能表

6、设计实验及原理

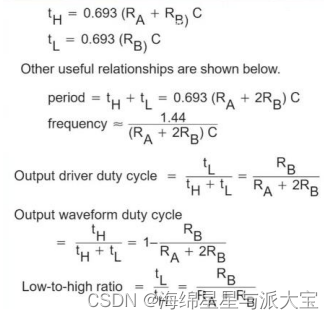

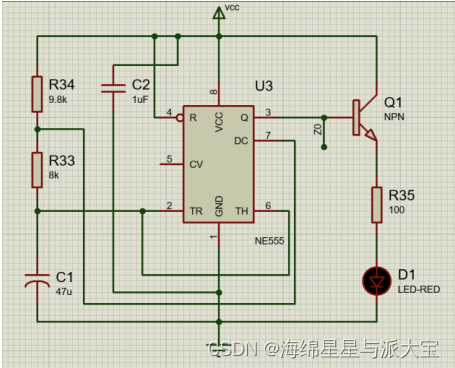

(1)振荡电路

在实际中,是没有脉冲激励源的,所以我们需要自己制作脉冲发生器(晶

振电路或多谐振荡电路),如图为一个 NE555 多谐震荡电路,通过电容的充放

电实现信号的上升下降,从而实现脉冲的上升下降。通过改变两个电阻和电

容的关系来改变频率。其计算公式及电路图如下:

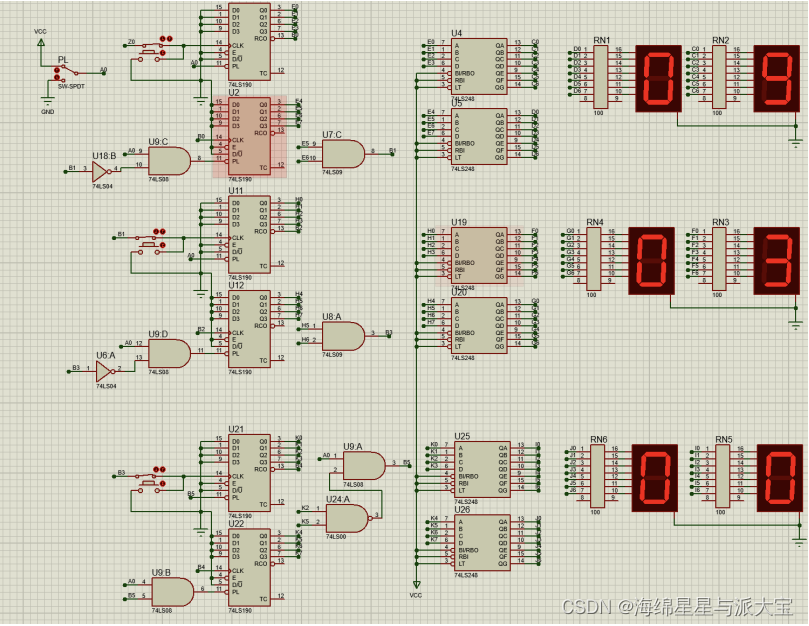

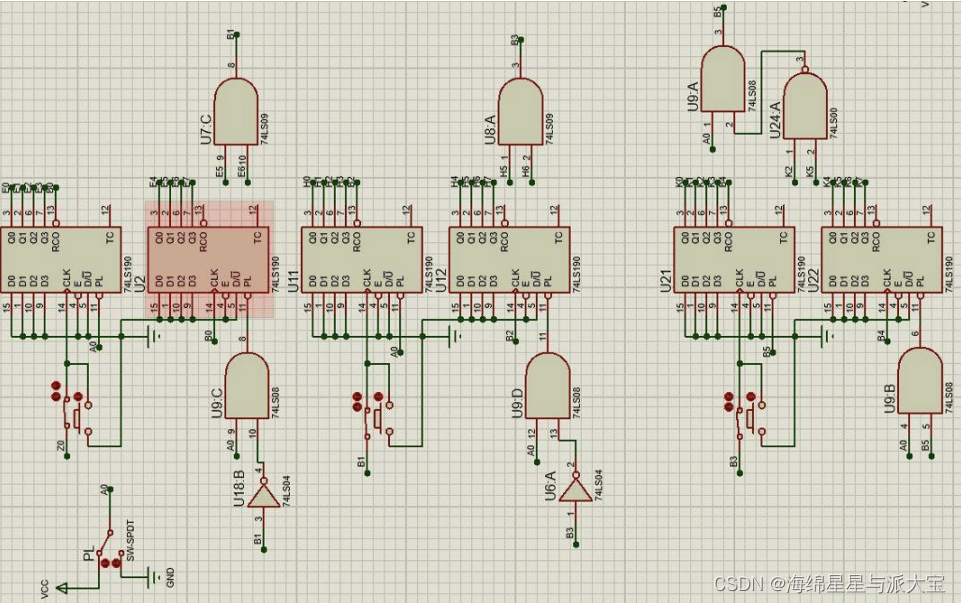

(2)计时器

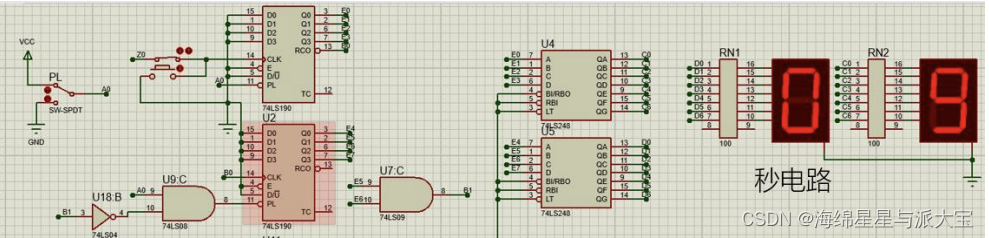

60 进制秒计数器的 CLK 接振荡电路的输出端,60 进制分计数器的 CLK

接 60 进制秒计数器 RO,24 进制时计数器的 CLK 接 60 进制分计数器的 RO,

当秒计数器显示 59 时进位,分计数器加 1,秒计数器显示 0,时计数器相似

(当时计数器显示 23 时,下一位则进位,所有计数全部置 0)。电路图如下:

(3)校时电路

在数字时钟与实际时间有偏差时,可以通过断开时、分、秒 CLK 之前的

开关,再按按钮对时间进行效准。电路图如下:

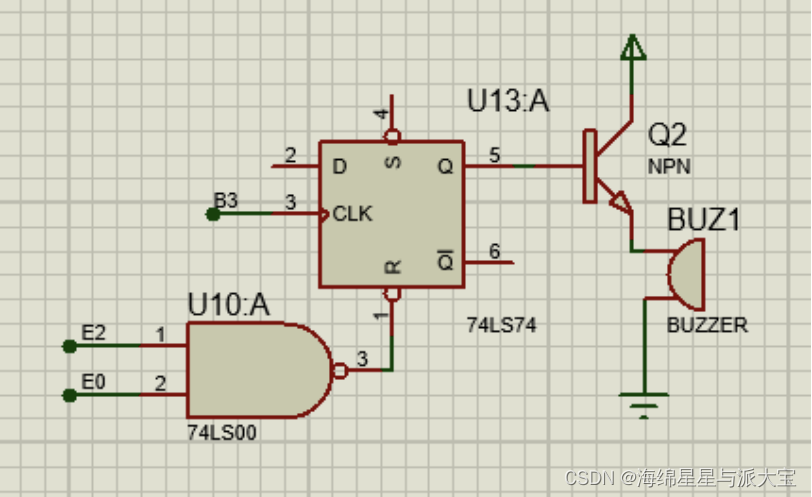

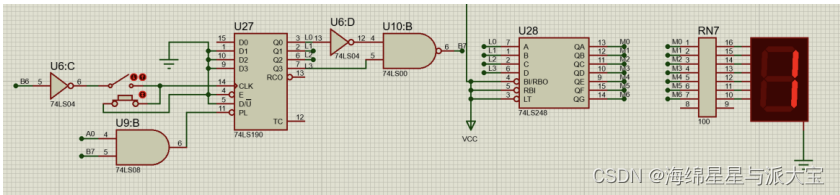

(4)整点报时

D 触发器的 CLK 端接分到时的进位端,当分为 60 的时候有进位信号,这

是 Q 反转为高点平,三极管导通,蜂鸣器响秒的个位计数器的 E2、E0 输出端

与非接到 D 触发器的复位端(当秒计数为 5 秒时,D 触发器复位,Q 为 0,

三极管不导通,蜂鸣器停止响,从而实现准点报时,持续时间为 5 秒)。电路

图如下:

(5)增加日期显示

星期计数器的 CLK 端接时计数器的进位端,23 时 59 分 59 下一位就产生

进位。电路图如下:

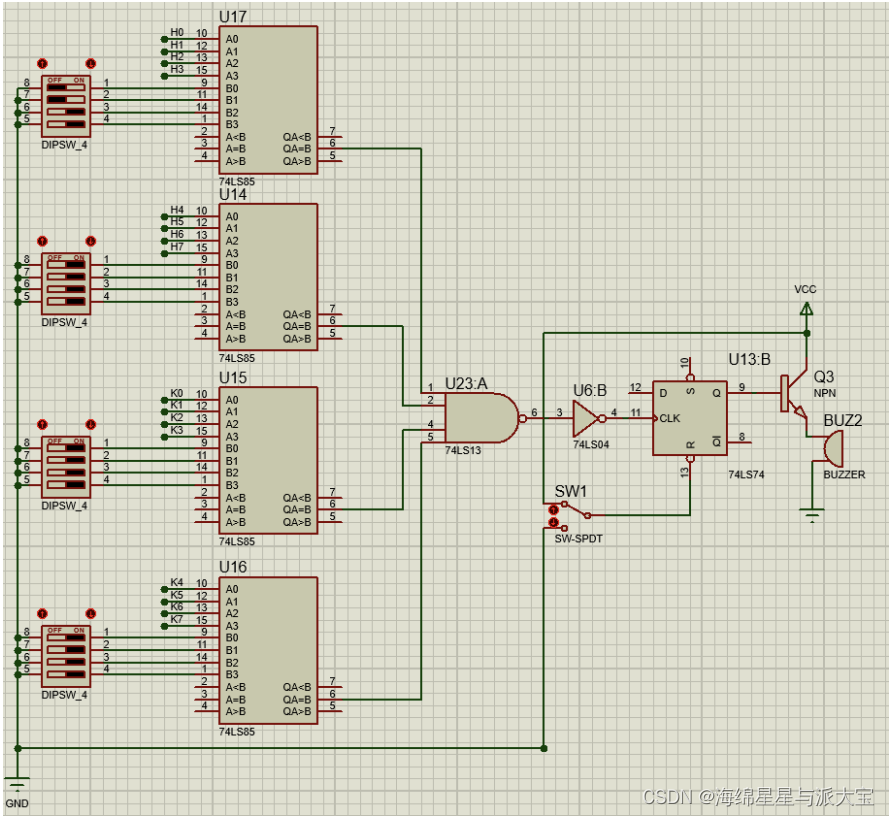

(6)定时功能

运用四个比较器,分别接到分、时计数器的输出端,再通过四个 4 位开

关输入定时时间(以 8421BCD 码的形式进行取数),一个开关接到 D 触发器

的复位端,再开关打开的情况下,当四个比较器输出高电平,CLK 为上升沿,

Q 变为高电平,三极管导通蜂鸣器响,这时将开关打下,D 触发器复位,Q

输出为低电平,三极管不导通,蜂鸣器停止响,这就实现了打开和关闭定时

的功能的效果。电路图如下:

转自:https://blog.csdn.net/qq_67233808/article/details/125911943