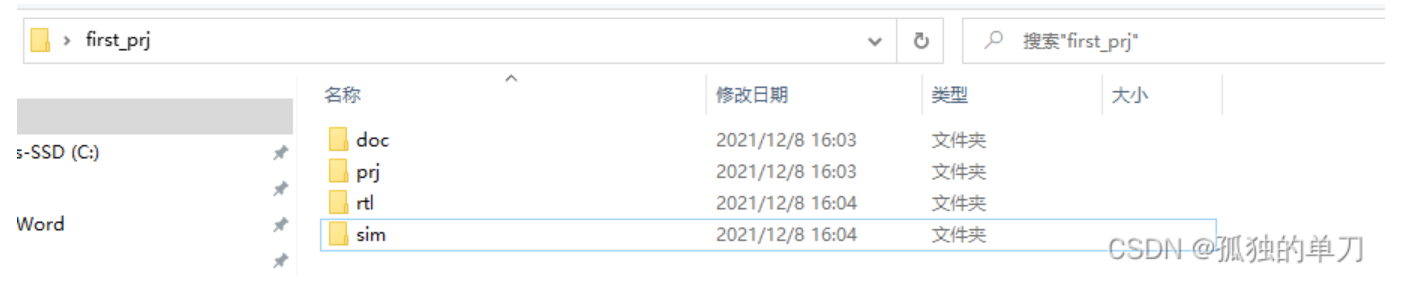

1、规范的文件夹

规范的文件夹划分管理也是十分重要的,若是把所有文件,例如设计文件、设计表格、图片、Quartus工程相关文件、仿真文件等不同类型的文件都统一放在一个目录下,将会使得整个文件夹臃肿不堪,而且后期找起文件来也非常不方便。所以推荐大家首先根据功能划分不同的文件夹来放不同的文件。

对于初学者,个人比较推崇的是正点原子推荐的4个文件夹的划分方法:

doc:主要放设计文件、设计图表、需求文件等一系列设计类文件,根据个人需求还可以进一步划分,如图片子文件夹、表类子文件夹等

prj:工程文件,主要放Quartus工程相关的文件,也可以再划分,如输出子文件夹、IP核文件等

rtl:主要放设计的Verilgo源代码,也可根据模块数量或类型继续划分成各个小的子模块,每个模块放相关的代码文件

sim:主要放仿真相关的文件,可以继续划分,如仿真文件testbench、仿真结果图片,生成的仿真数据txt等

本文是要带大家新建一个Quartus II的工程,所以我们给这个工程随便起个名字,既然是第一个工程,就叫first_prj吧。我们新建一个first_prj文件夹,然后在下面新建上面说的4个子文件夹,如下:

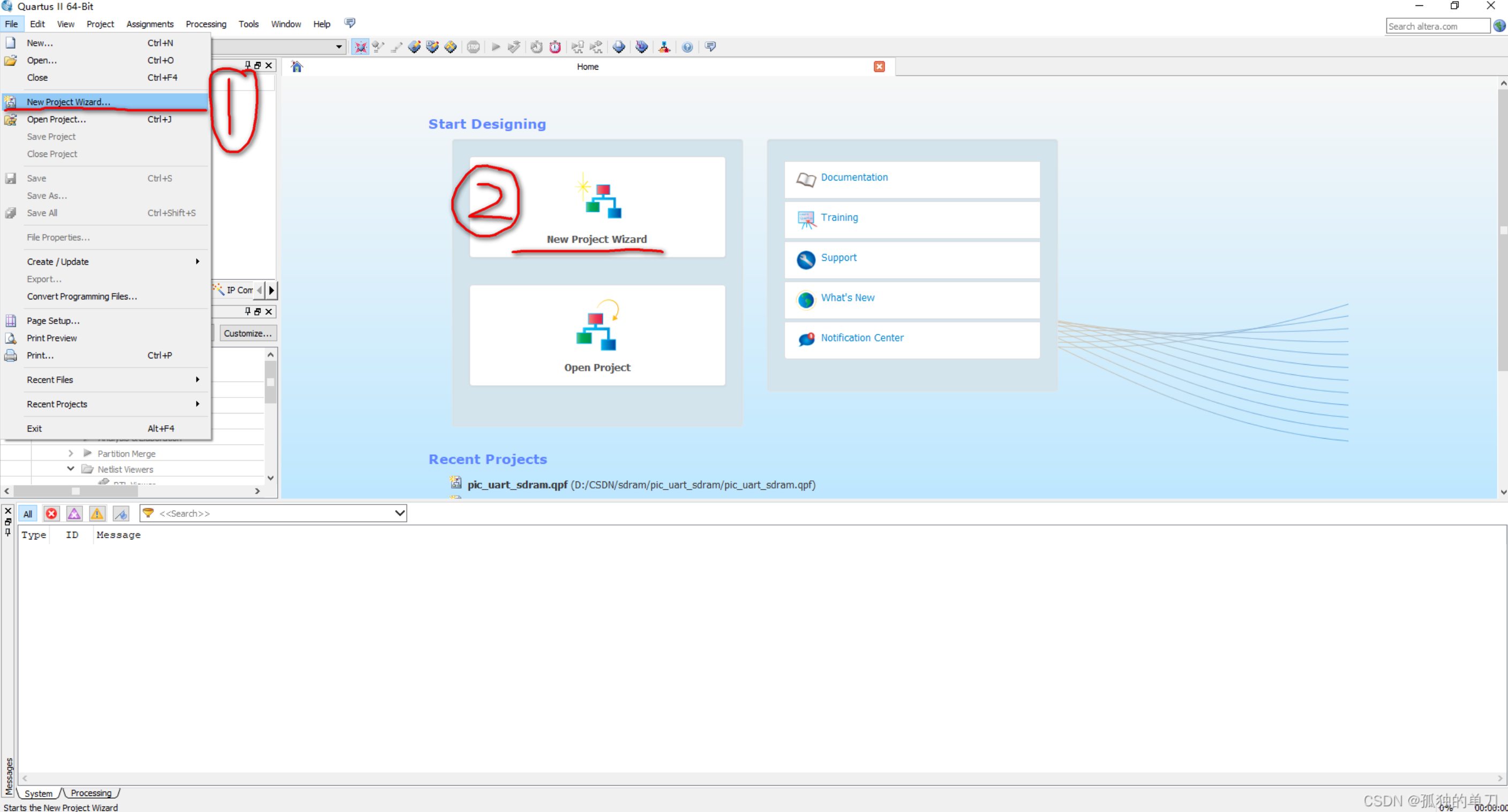

2、新建工程

打开Quartus II软件,新建一个工程有两种办法:1、点击file—-new project wizard;2、直接点击 new project wizard。如下所示:

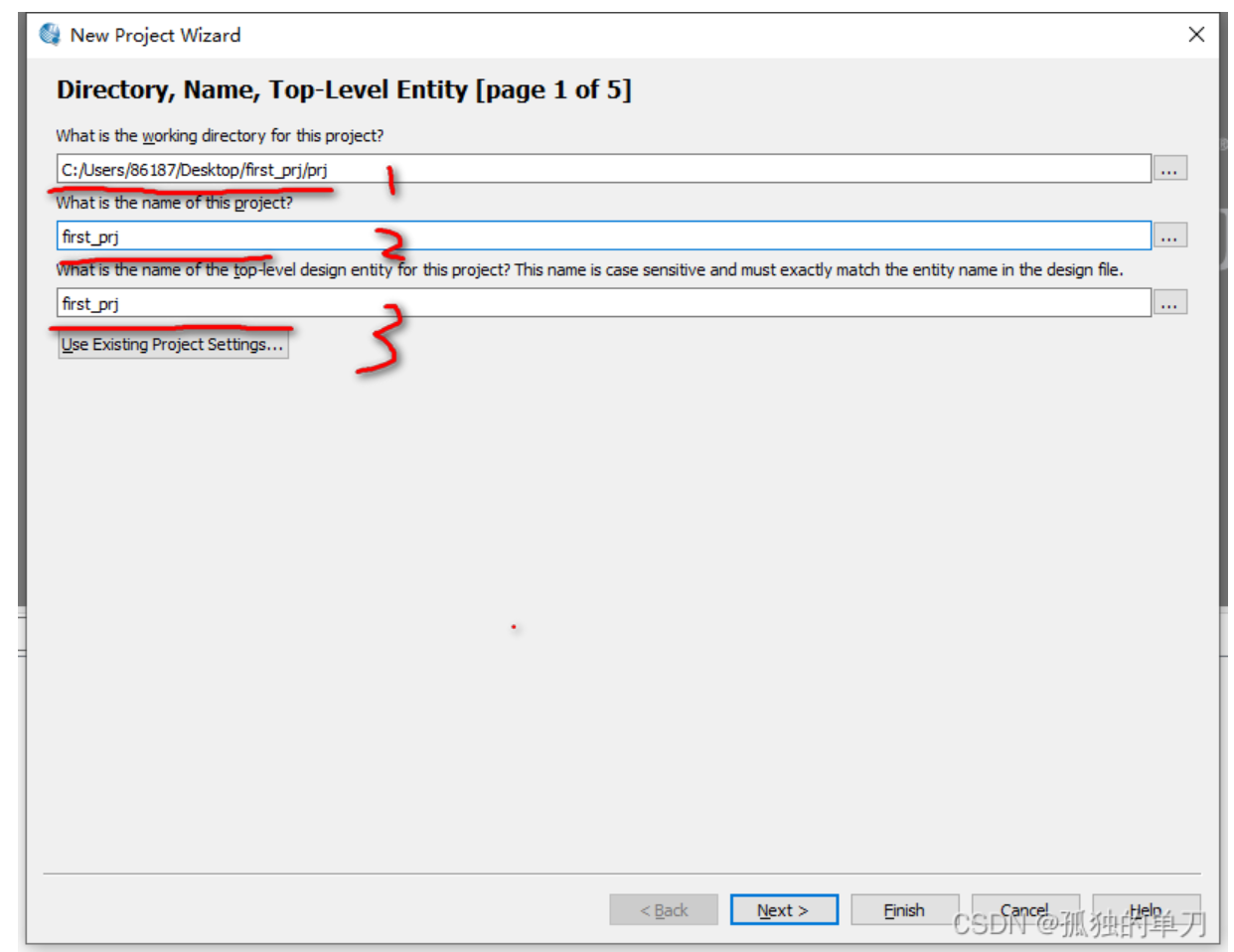

然后出现下面的界面:1、是我们工程的存储路径,选择文件夹first_prj/prj这个文件夹;2、是工程名字,之前已经想好了,工程名叫 first_prj;3、是顶层模块的设计名(这里说下,在复杂点的工程中一般有很多个设计文件,编译器为了很快的找到哪个文件是最顶层的文件,所以需要在工程建立阶段指定顶层文件的名字),建议是与工程保留一致即可,方便管理。

设置完后,点击next,进入下一页的配置

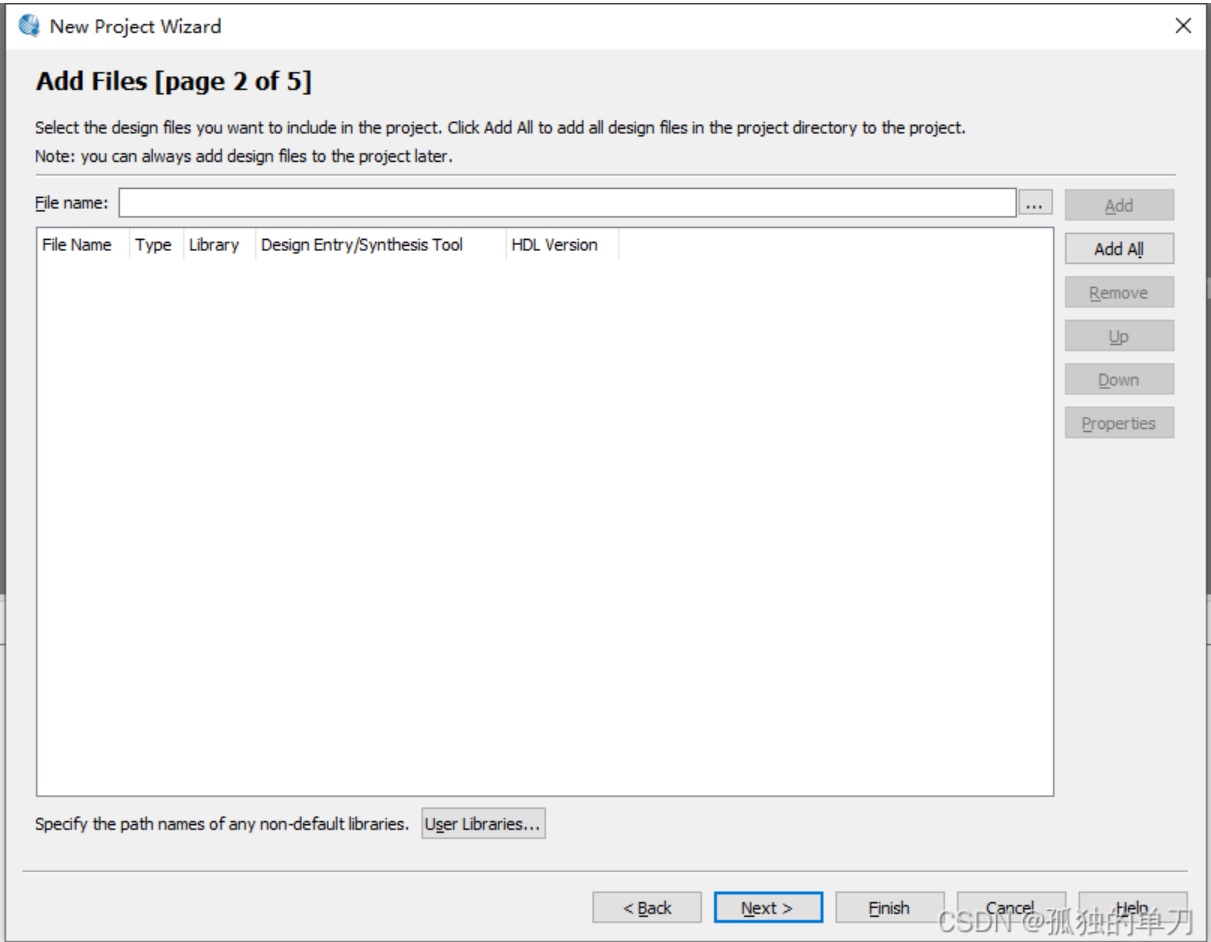

下面这一页是添加设计文件到工程中,如果设计文件已经写好了,可以在这一环节添加到工程,如果没写好也不要紧,后面再添加就是的。因为我们还没有设计文件,所以直接next

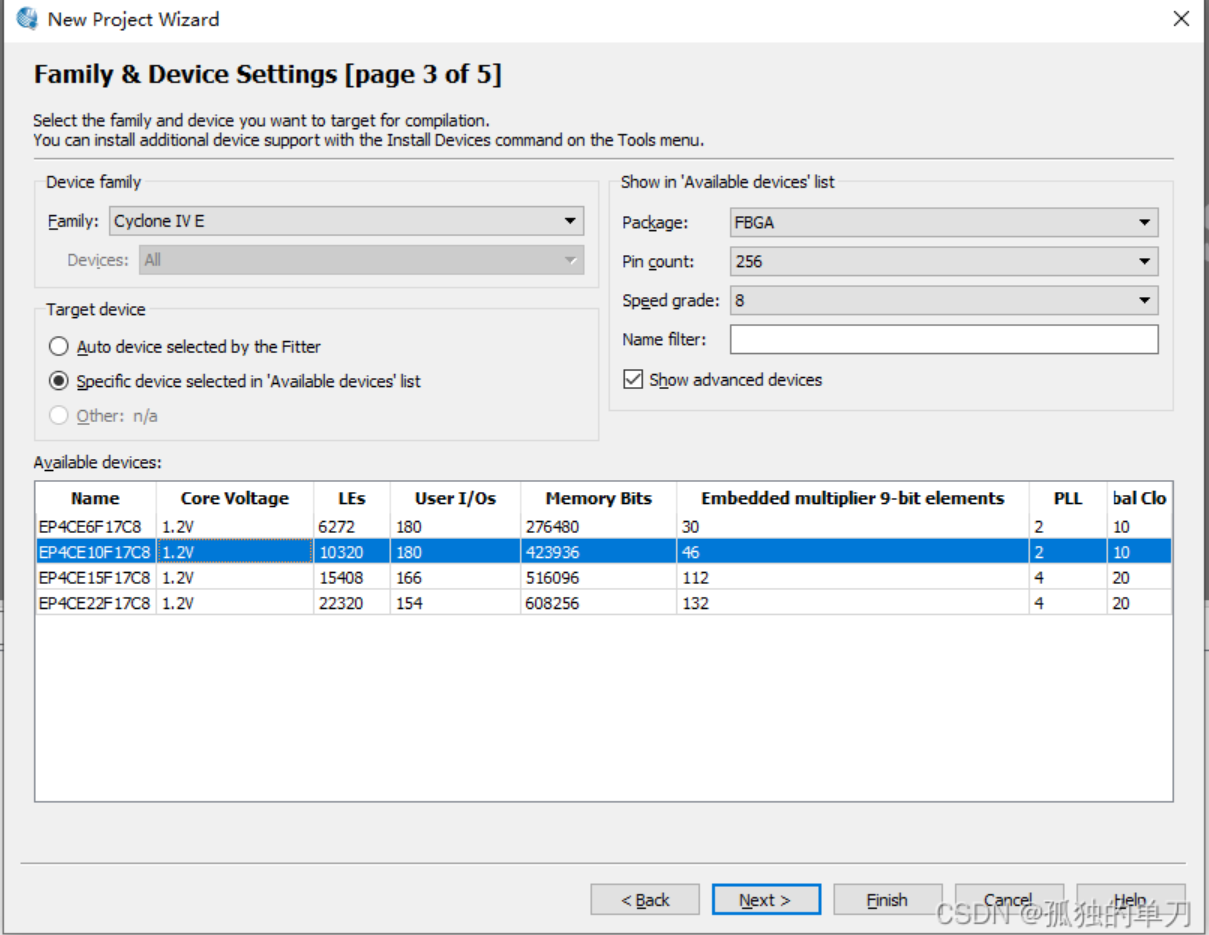

下面这一页是选择使用的FPGA信号,这个对照自己的FPGA芯片信号选择就可以了,我贴出我所使用的开发的芯片型号如下:

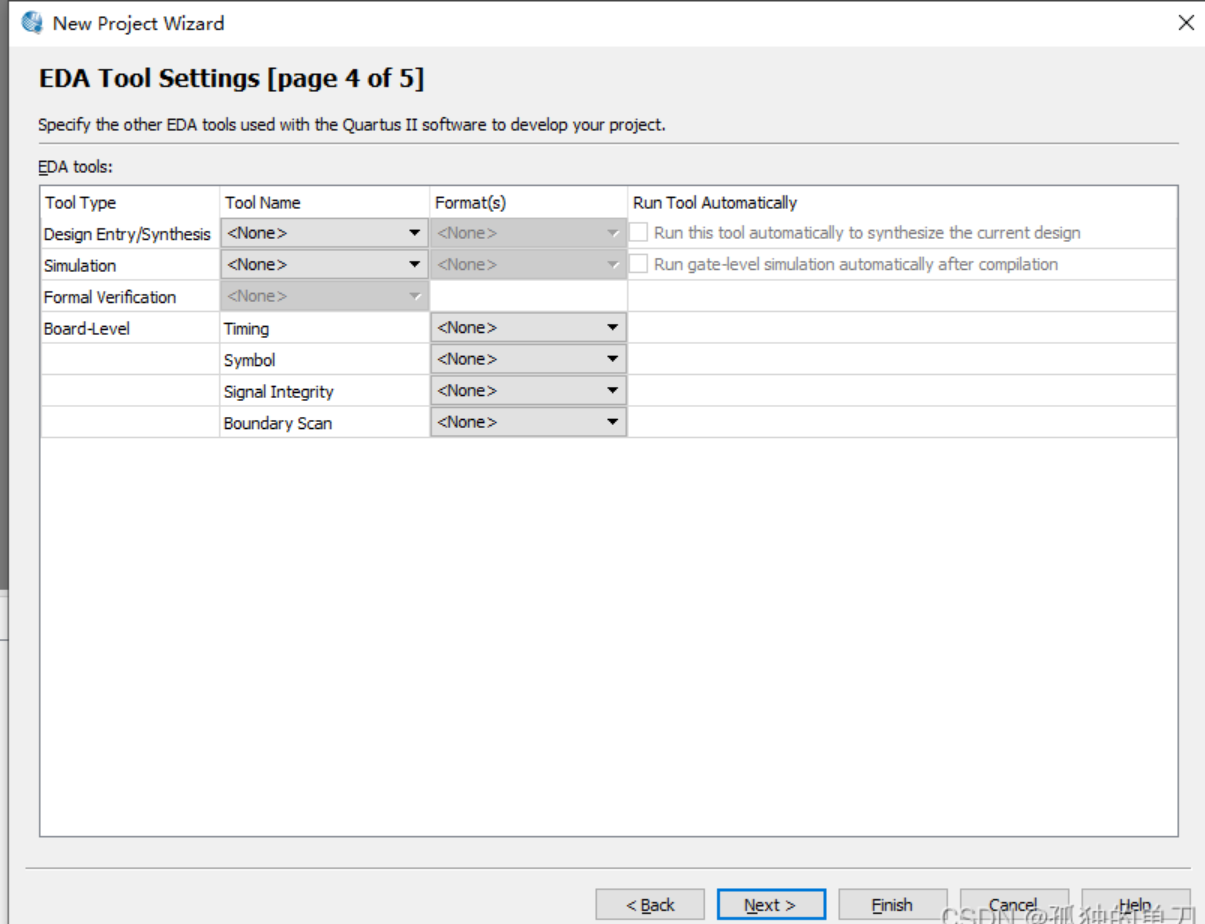

下面这一页是选择使用的第三方的EDA工具,我们初学者别搞得这么花里胡哨的,先把最基本的功能给学会再说,直接不管,点击next

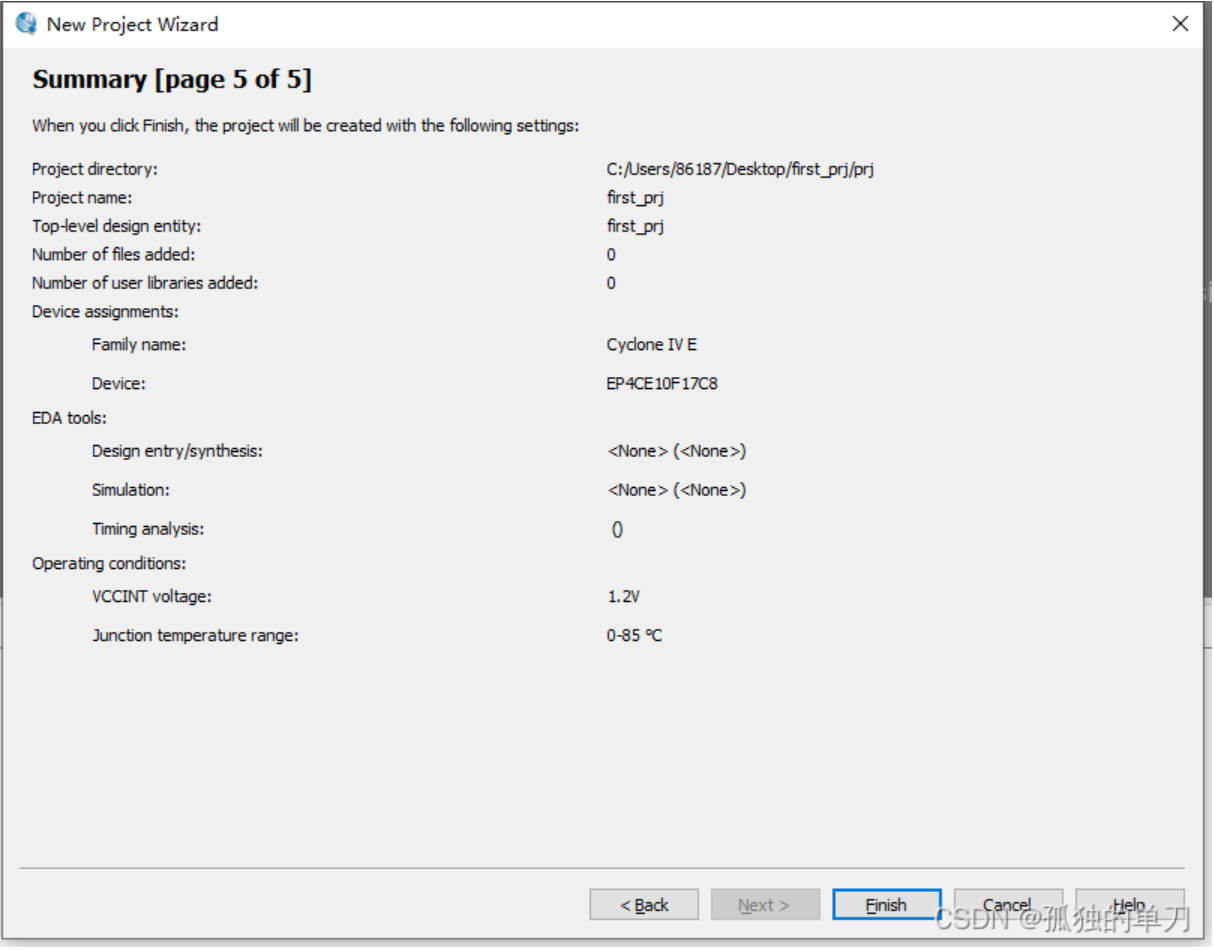

下面这一页是我们工程的一些信号的总览。看下就可以了,然后点击finish

至此,一个基于Quartus II的工程就算建好了。但是这只是个空壳子,因为在我们的工程里什么都还没有,接下来就添加一下设计文件。

3、Verilog代码编写

我们可以先写好一个Verilog代码后,添加到工程里面,也可以直接在Quartus界面新建一个.v文件,然后将其编写好。我这里示范第一种方法。

在文件下first_prj/rtl 下新建一个txt文件,命令为first_prj.txt,然后将后缀改为.v,这样该文件就变成了一个Verilog类型的设计文件。双击打开,输入如下代码(目的是点亮一个led灯):

module first_prj( input clk , //输入时钟 input rst_n , //低电平有效的异步复位信号 output reg led ); always@(posedge clk or negedge rst_n)begin if(!rst_n) //当复位时 led <= 0; //led灭 else //其他时候 led <= 1; //led亮 end endmodule

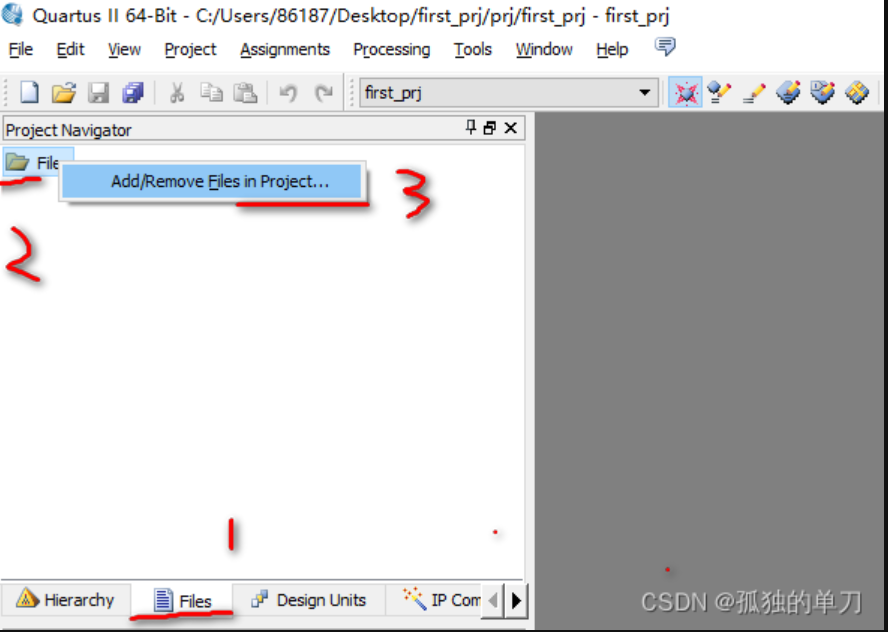

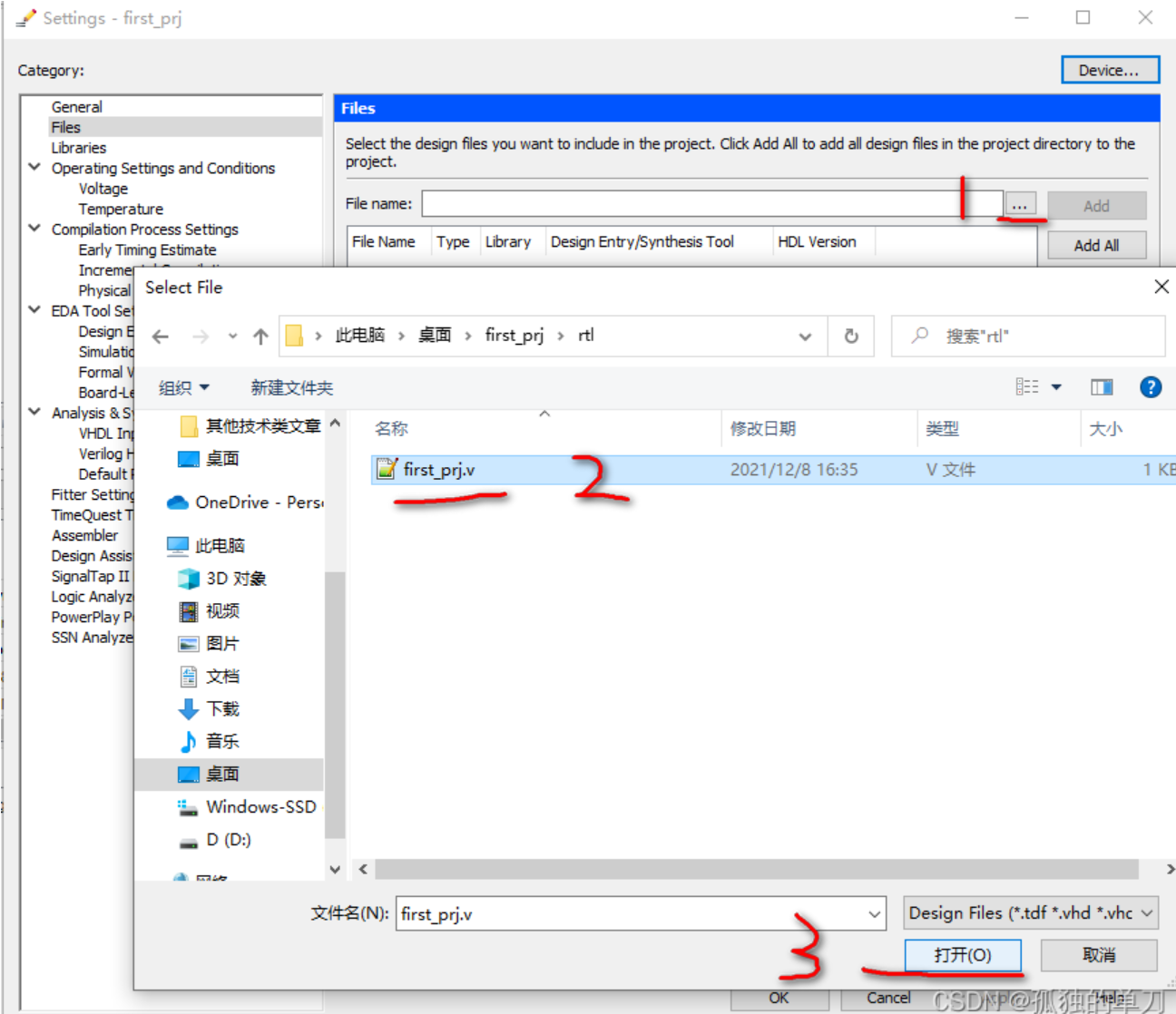

然后按下图的顺序打开文件添加到工程的选项卡:

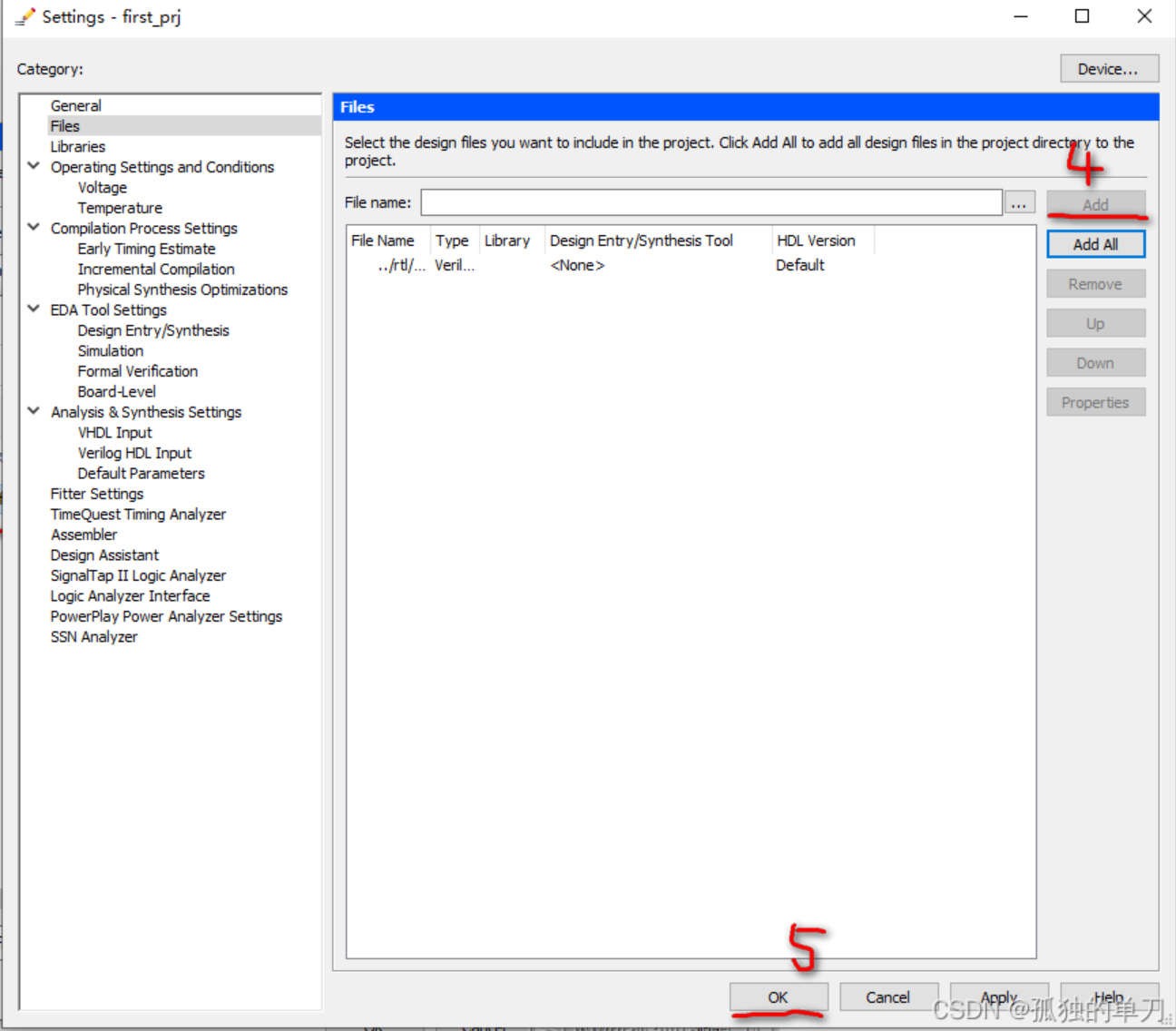

按下列步骤添加我们的设计文件:

现在我们的工程中就有了一个设计文件了,接着进行下一步。

4、编译

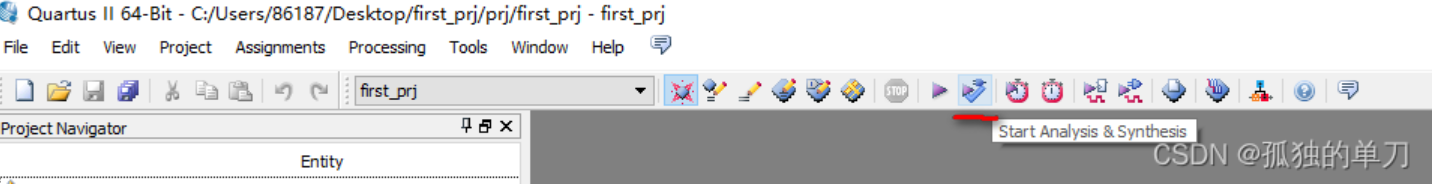

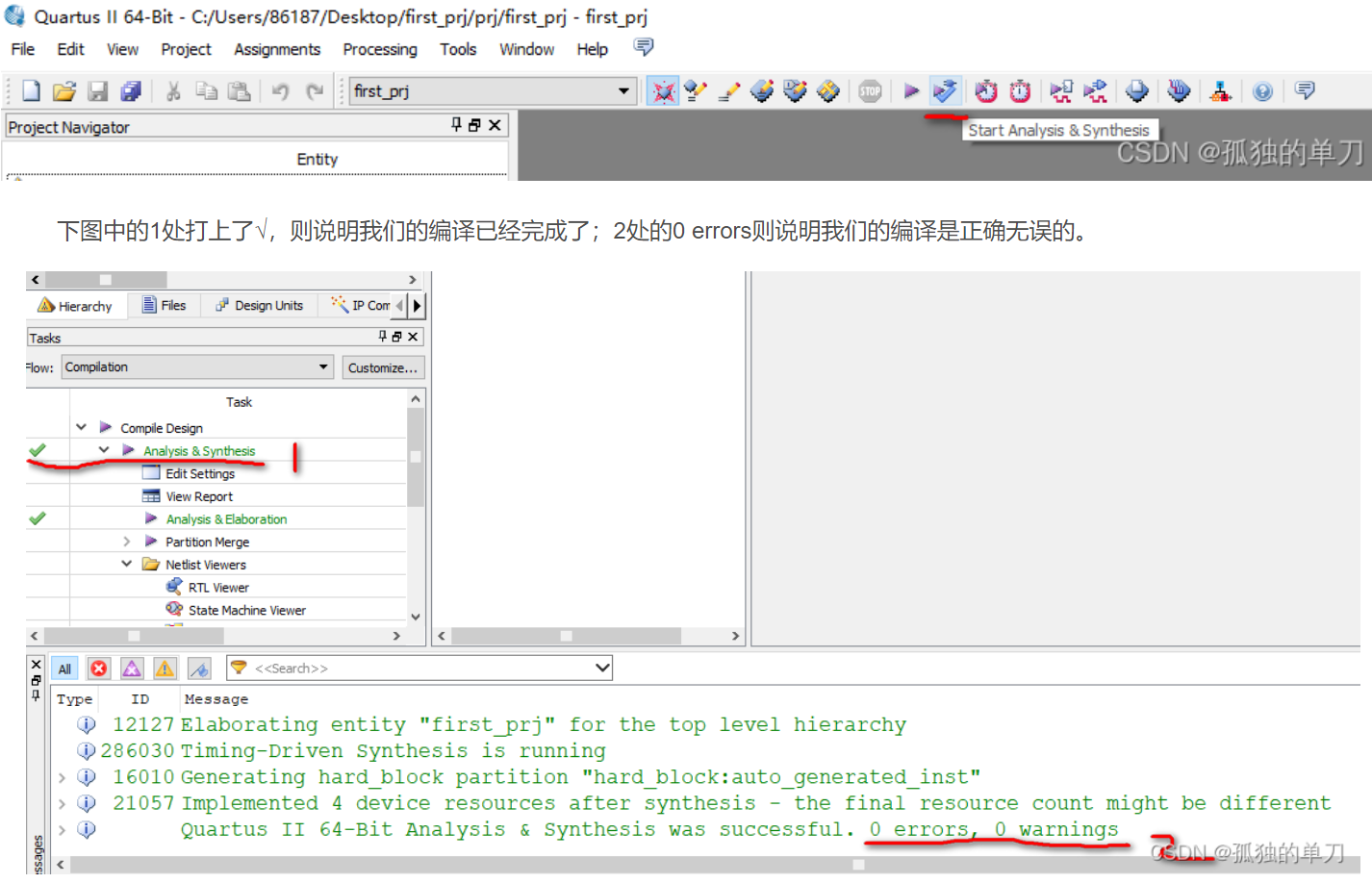

点击下图的图标进行代码的分析和编译,该步骤的目的是首先检查语法是否有错,其次是综合器将代码解释为电路的形式。

下图中的1处打上了√,则说明我们的编译已经完成了;2处的0 errors则说明我们的编译是正确无误的。

5、管脚绑定

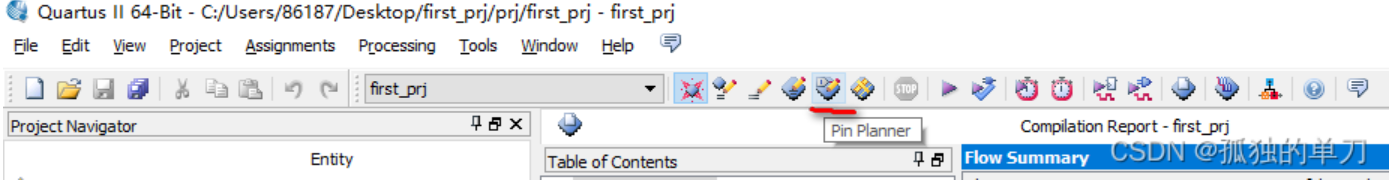

在上板 之前还需要进行引脚约束,就是根据硬件原理图确定输入时钟、复位与输出led是对应FPGA芯片的哪个管脚(请查阅原理图)。如下图点击pin planner打开管脚分配界面:

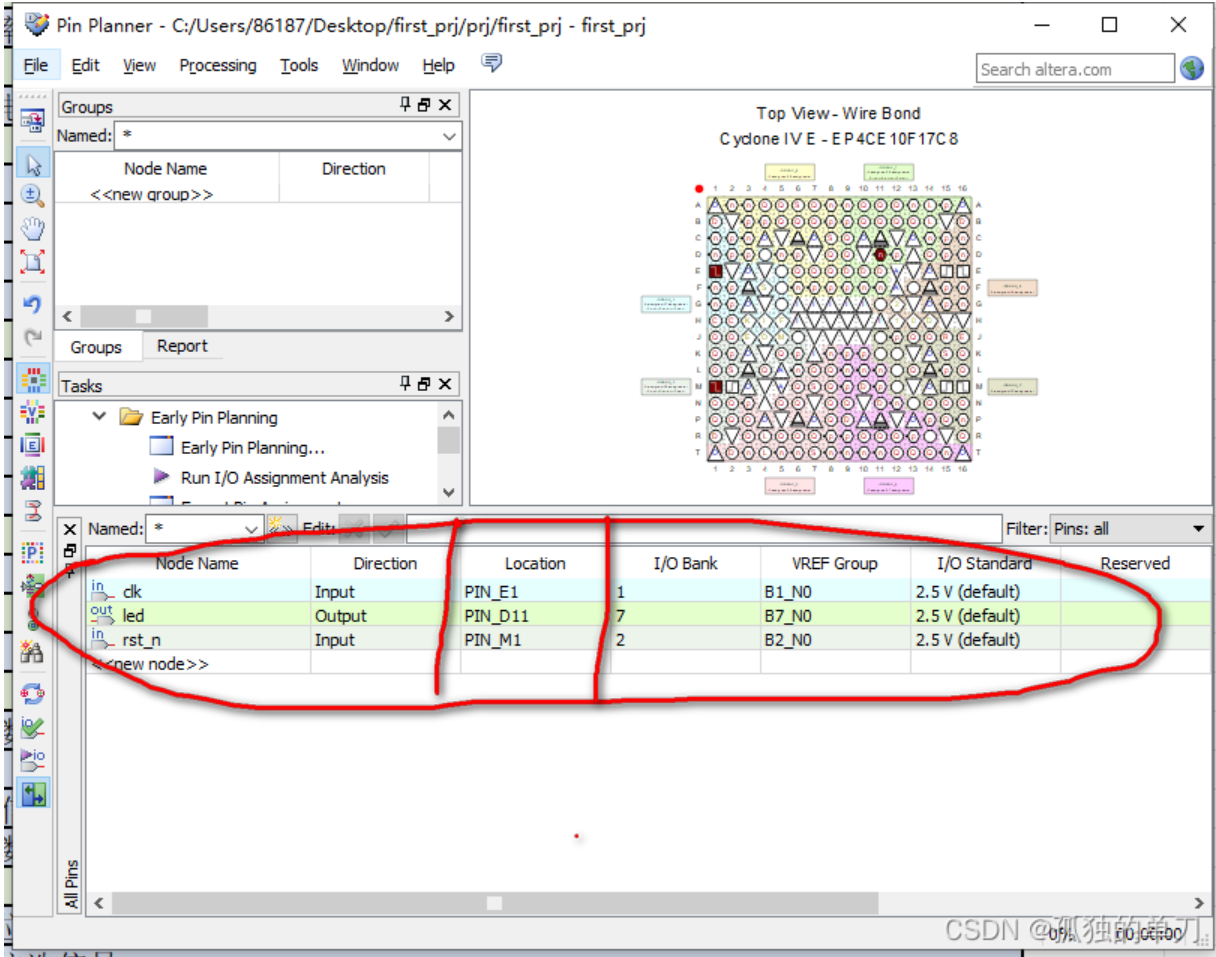

根据FPGA的具体管脚分别讲对应的芯片分配,如下:

6、全编译

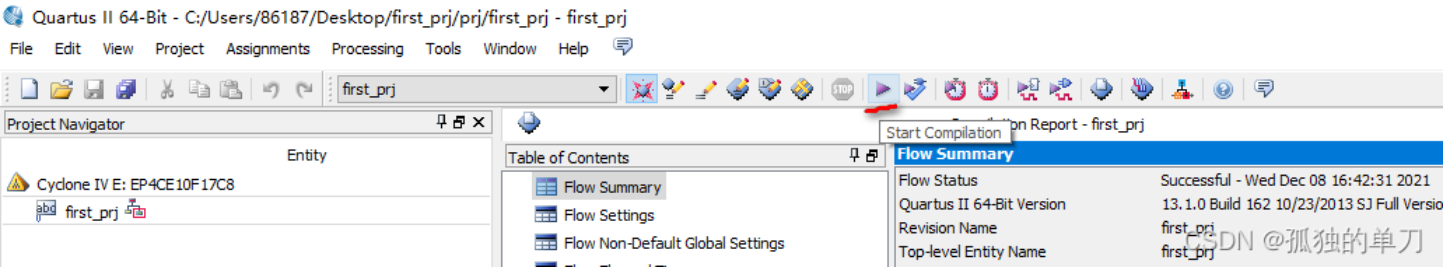

全编译和分析综合的不同是全编译需要进行布局布线,管脚绑定后就可以对全局进行布局布线了。点击下图的按钮进行全部的分析综合布局布线。

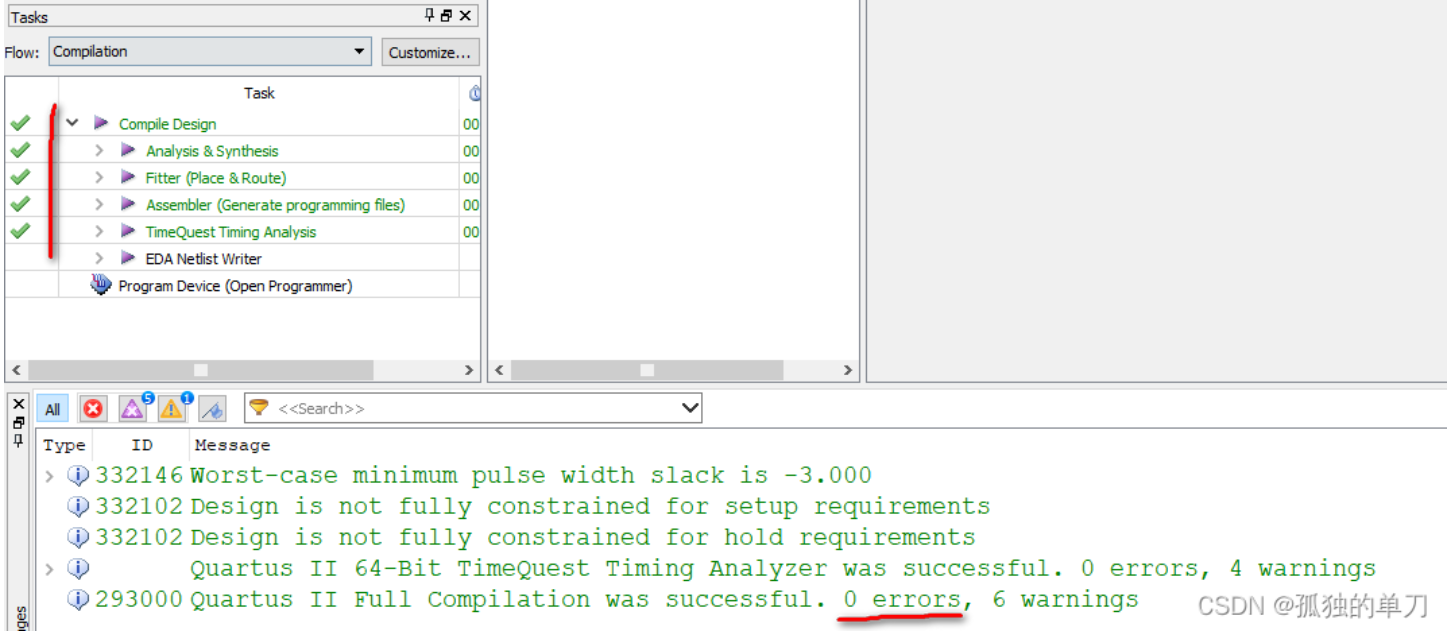

当界面如下时,则说明我们已经全编译完成了:左边的√表示全编译完成;后边的0 errors则表示全编译没有错误。

7、烧写下载文件

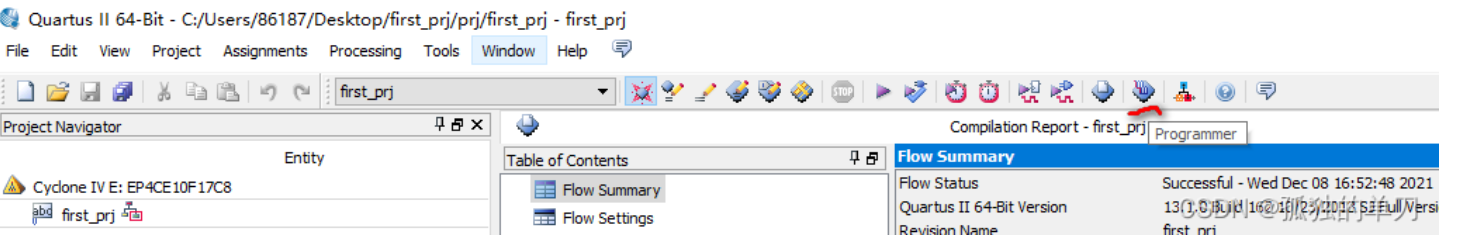

到这一步就基本完成所有的工作了,最后只需要把生成的sof文件给烧写到FPGA芯片里就可以了。如下图打开烧写界面:

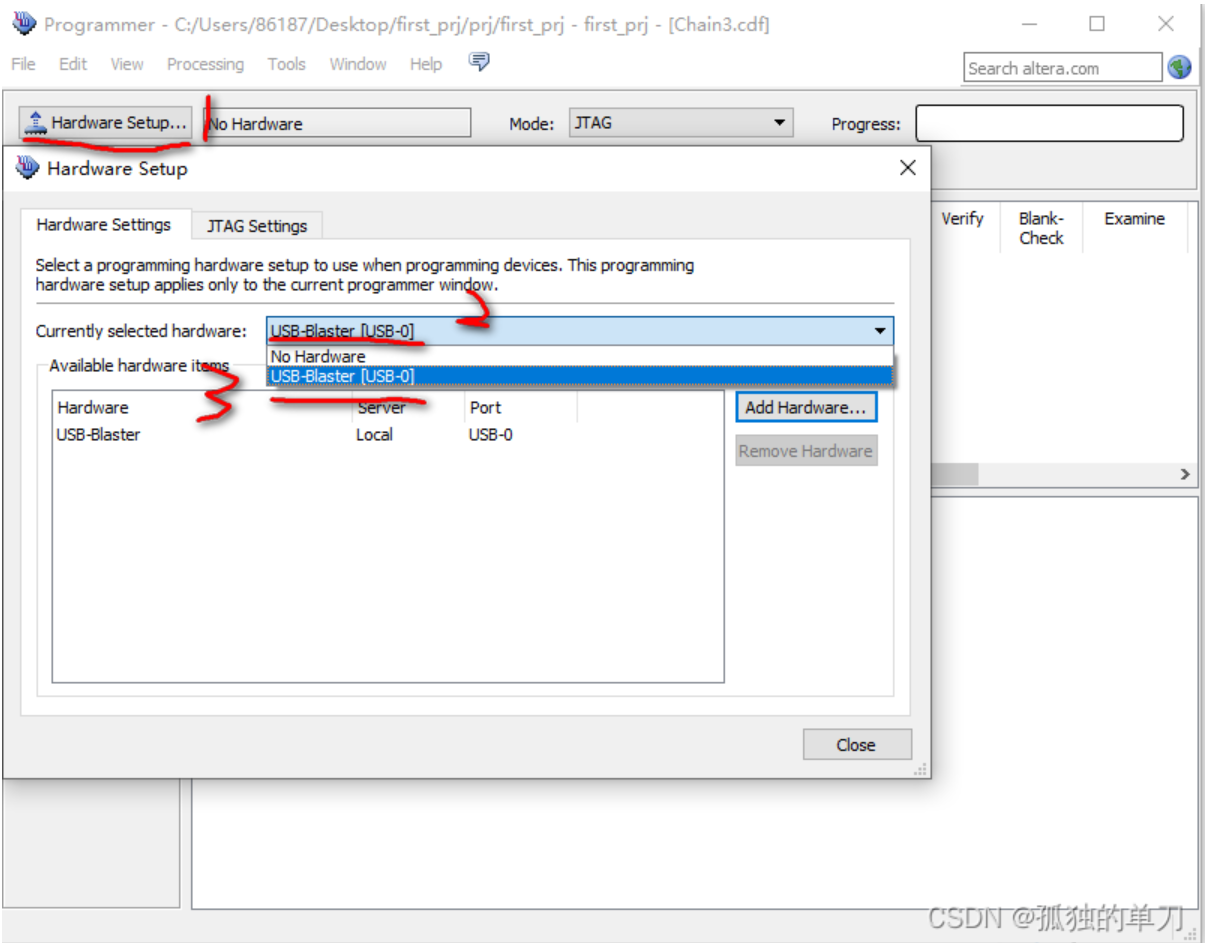

烧写界面如下,按如下步骤连上我们的板卡:

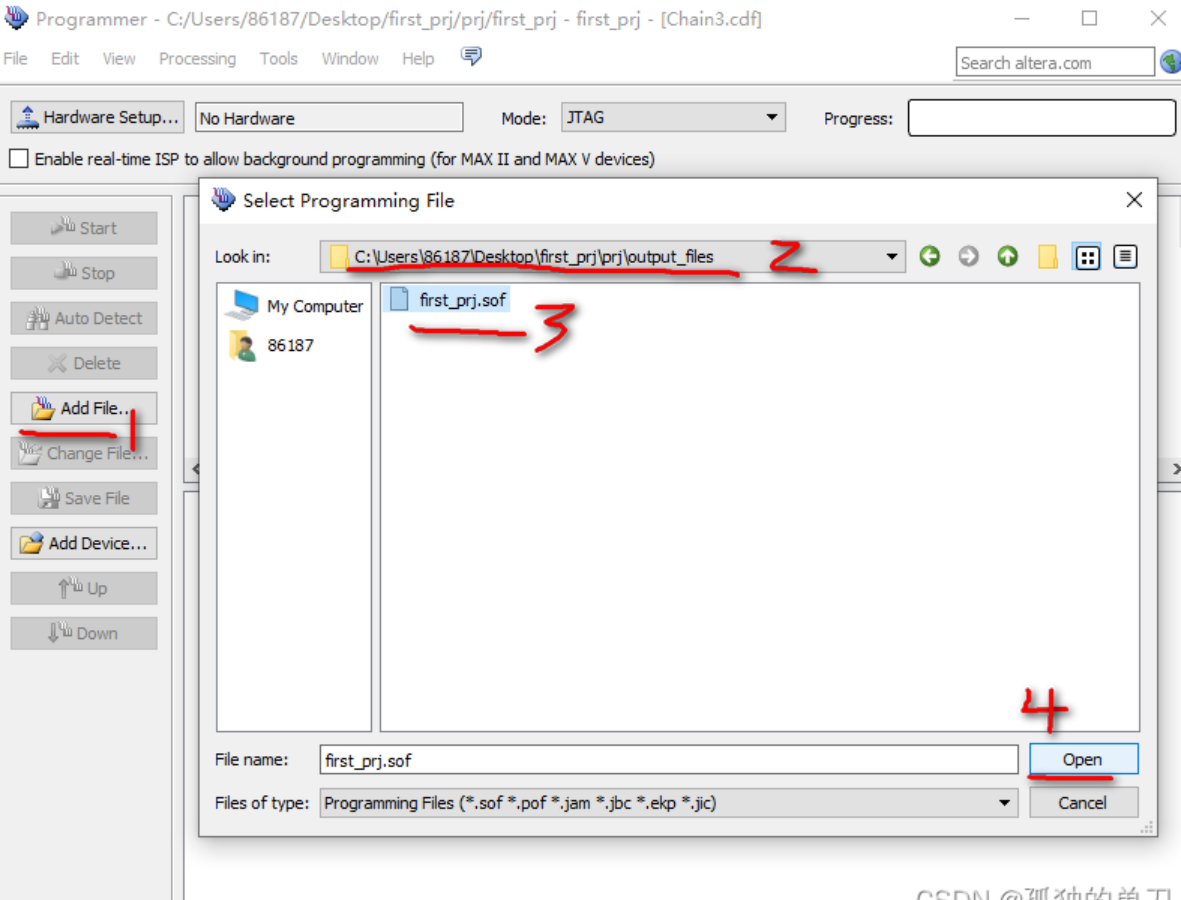

一般来讲,编译器会自动添加最后一次生成的sof文件,如果没有添加的话,我们按如下步骤添加:

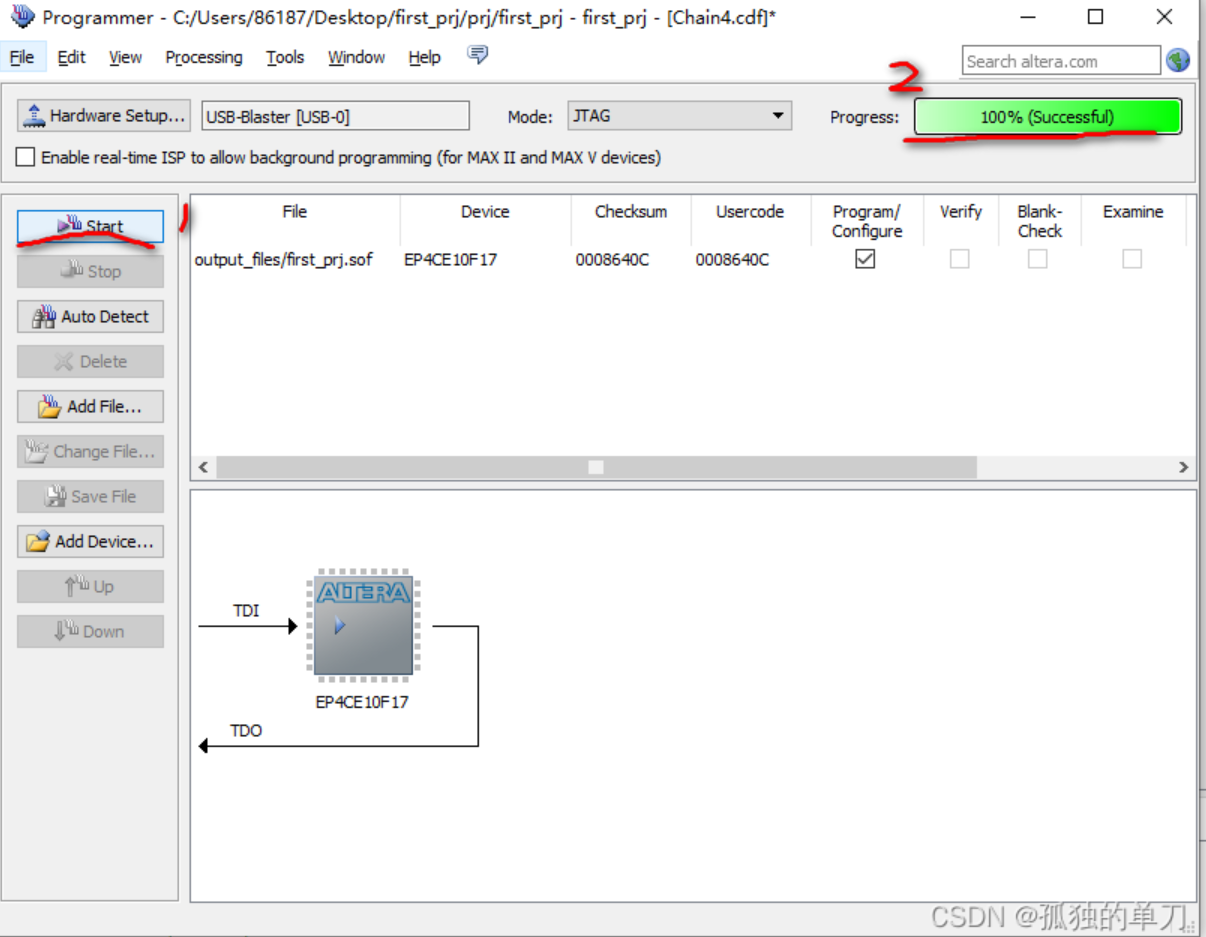

添加完成后,点击start,开始烧写程序,等到progress指令条到100%则表示烧写完成

8、实验现象

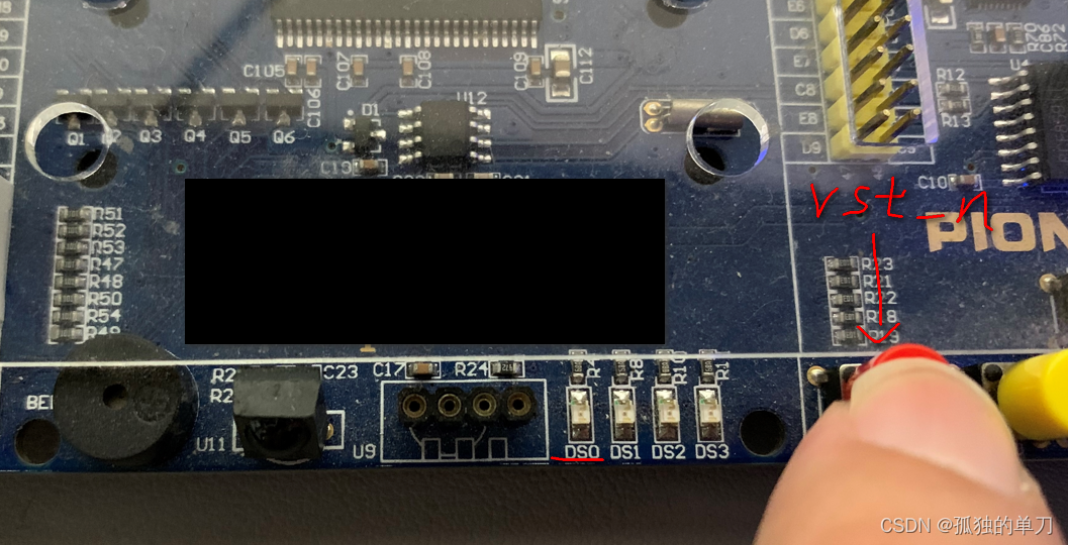

实验现象就是按下复位键,led灭;不按下复位键时,led常亮。

按下复位时:

没有复位时:

不错,与我们预期效果一致。所以新建第一个FPGA的工程就成功了!恭喜你,以后就正式上了FPGA开发的贼船啦!~~

9、其他

创作不易,如果本文对您有帮助,还请多多点赞、评论和收藏。您的支持是我持续更新的最大动力!

关于本文,您有什么想法均可在评论区留言。如果需要整个工程,请在评论留下邮箱或者私信我邮箱(注意保护隐私)。

自身能力不足,如有错误还请多多指出!

版本信息

文件:V1.0

编号:0001

Quartus II:Quartus II 13.1 (64-bit)

————————————————

版权声明:本文为CSDN博主「孤独的单刀」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/wuzhikaidetb/article/details/121793457