概述

本文选用的FPGA芯片是Intel(原Altera)的EP4CE6E22C8N,选它的原因是这个型号是个比较经典的型号,很多入门开发板都用它,

首先是老样子,先放上完整的参考原理图先,然后再一一的讲解,如下:

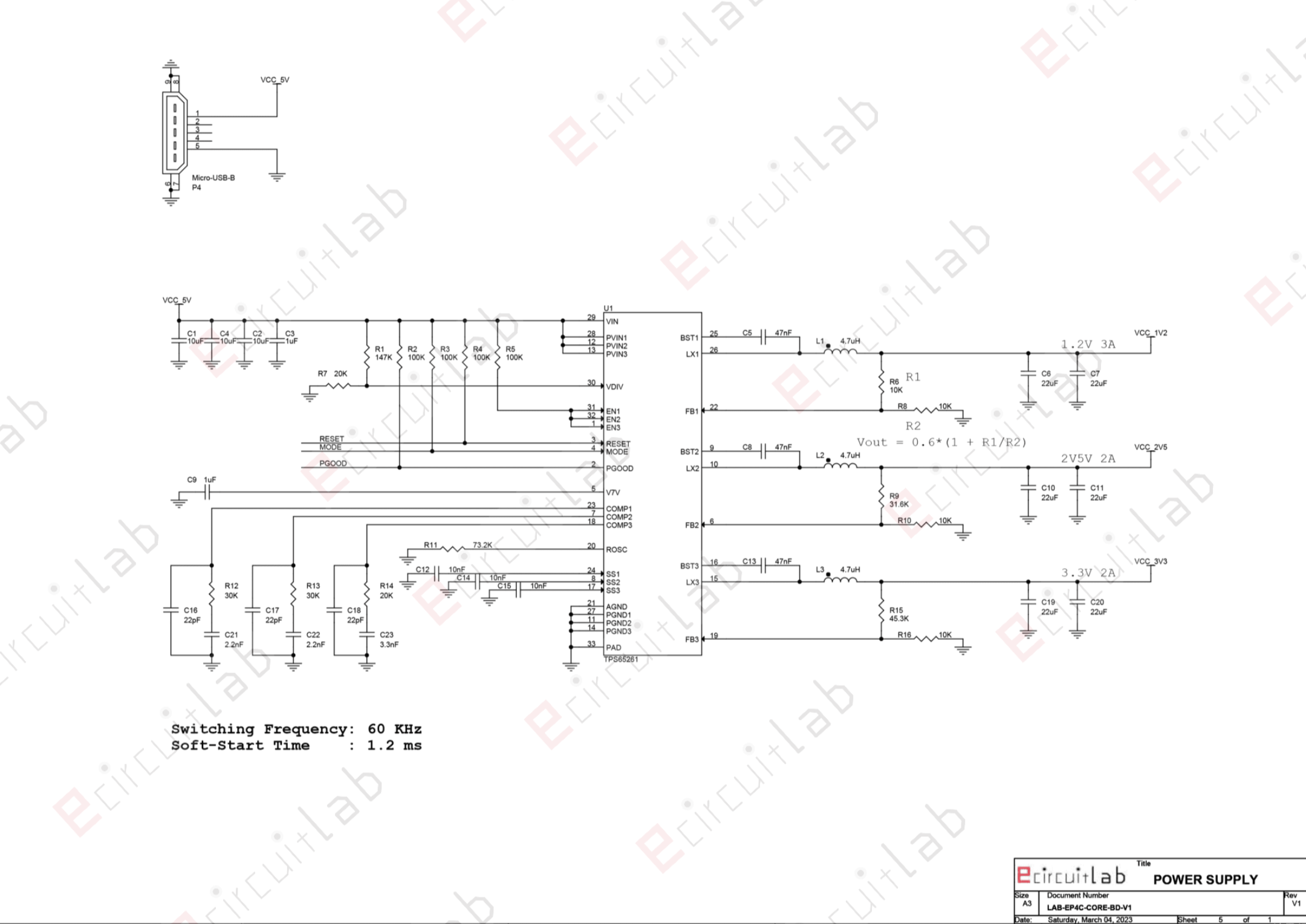

图1. FPGA最小系统供电电路

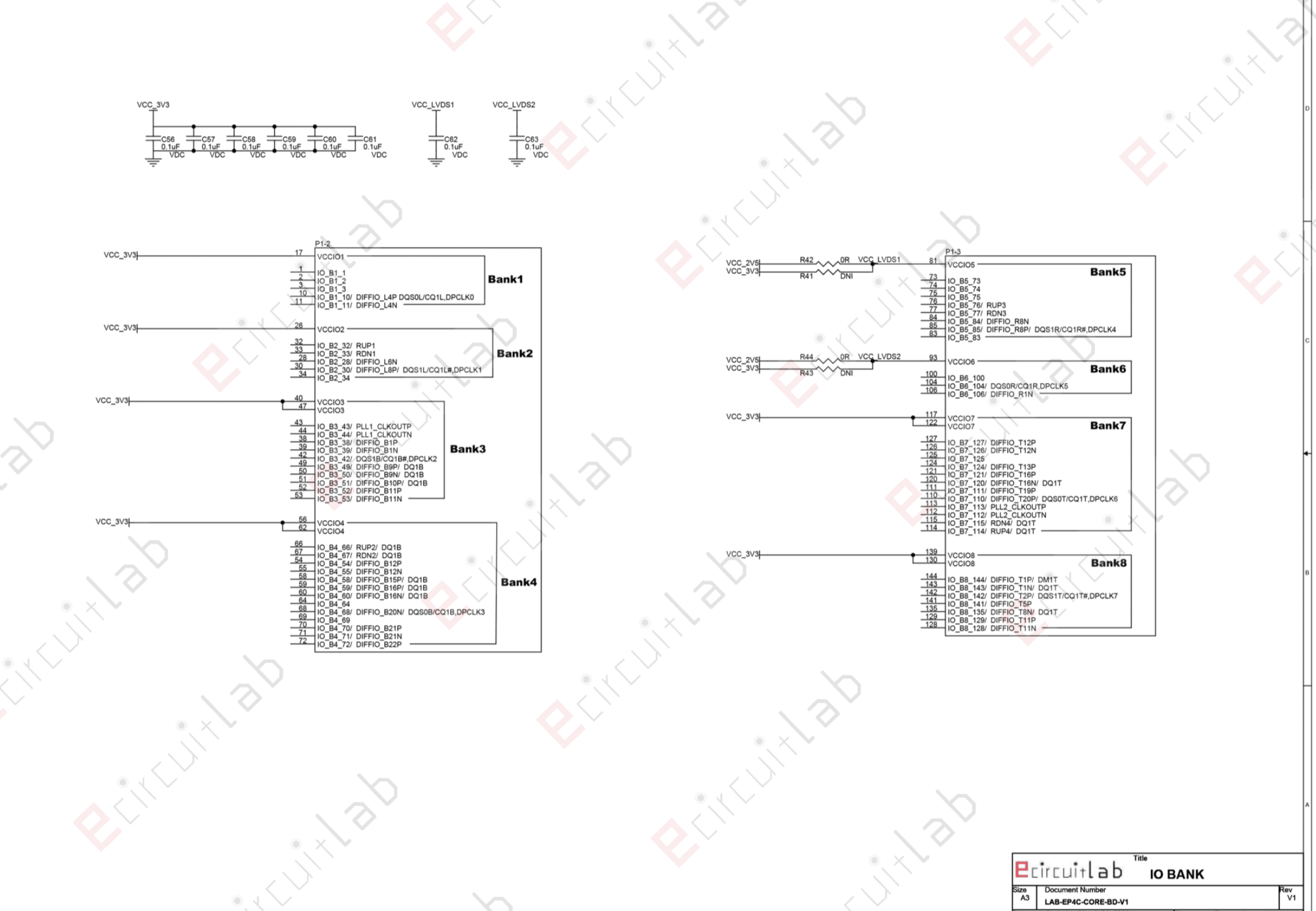

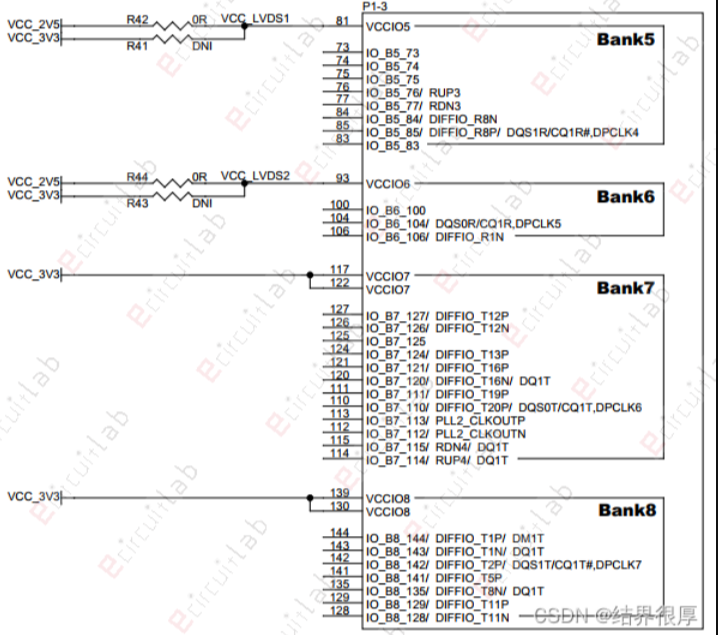

图3. FPGA BANK电路,IO没拉出去,可自行拉出去接到排针或者其他地方

设计详解

1. 电源设计

首先我们先来看EP4CE6E22C8N的供电,EP4CE6E22C8N属于Cyclone IV E系列,在官方的引脚连接指南资料里提供了电源设计的example如下图所示。

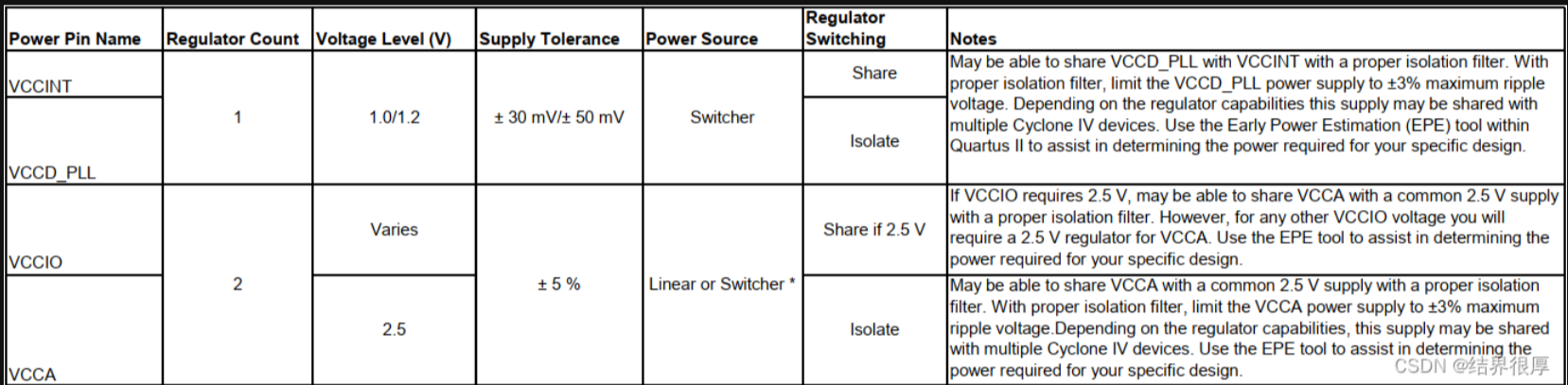

图4. 电源设计参考和相关指标

从上图可以知道,EP4CE6E22C8N有4组电源轨,各个电源轨的描述整理如下。

-

VCCINT、VCCD_PLL:

VCCINT、VCCD_PLL电压为内核电源和PLL的数字电路电源。电压支持1.0V/1.2V可选,允许的偏差分别为±30mV/±50mV,VCCINT和VCCD_PLL两组电源轨电压一样,供电虽然可以由一个开关稳压器提供,但要求VCCD_PLL必须用磁珠跟VCCINT隔离,VCCD_PLL对电源纹波要求非常高,最大纹波必须控制在±3%以内,超出这个范围可能导致PLL工作异常,比如时不时失锁啥的。

-

VCCA:

VCCA是给PLL的模拟电路供电的,使用2.5V供电,电源纹波一样要求控制在±3%以内,否则也容易出各种奇怪问题。

-

VCCIO:

VCCIO是给FPGA各个BANK的IO供电的,Cyclone IV E的VCCIO支持1.2V、1.5V、1.8V、2.5V、3.0V、3.3V几种电压。

在看FPGA的手册时我们会看到BANK几BANK几这样的描述,这个BANK到底什么意思呢?FPGA跟我们常接触到的MCU、MPU、CPU不同,它是数字电路可编程芯片,为了满足数字电路可编程,要应付很多数字电路方案,不同方案的外设IO电平可能不同。所以设计了IO支持多种电压,然后再分成多个组,不同组之间可以电压不一样,每个组叫一个BANK,这样的话就可以实现一颗芯片支持多种IO电平,芯片不会因为外设IO电压不匹配再去搞一堆电平转换。

电源供电电路设计:

上面我们分析了EP4CE6E22C8N的电源轨,对于芯片的正常工作我们知道,至少要有1.0V/1.2V给VCCINT、VCCD_PLL供电,2.5V给VCCA供电,至于VCCIO,需要看我们外设电平情况,因为这里是最小系统,就不考虑实际外设情况,直接把所有IO都设计为3.3V电平。

FPGA跟我们常规接触的MCU不同,规格书里没有功耗信息给我们去评估每个电源轨的供电电流情况,通常需要FPGA工程师提前把RTL工程做好,进行电路综合后给出每个电源轨的功耗信息,然后我们再在这个信息上留适合的裕量来选择供电方案。

对于EP4CE6E22C8N来说,最糟糕的情况下,VCCIN的峰值电流在2A左右,VCCD_PLL和VCCA一般都在400mA以内,VCCIO比较小,每个BANK的IO电流最大一般也都是100mA左右。

这样总结下来这里选择TI的TPS65261,它集成了3组BUCK方案的控制单元,3个通道支持连续输出电流分别是3A、2A、2A,跟我们需求非常贴近,参考规格书的纹波信息,输出在满载情况下纹波也非常小,符合FPGA的电源要求,如下。

图5. TPS65261通道1满载时的纹波信息

参考TPS65261规格书信息设计的最终电路上面图1所示,通道1输出1V给VCCINT和VCCD_PLL供电,通道2输出2.5V给VCCA供电,通道3输出3.3V给VCCIO供电,总电源5V通过Micro-USB口输入。

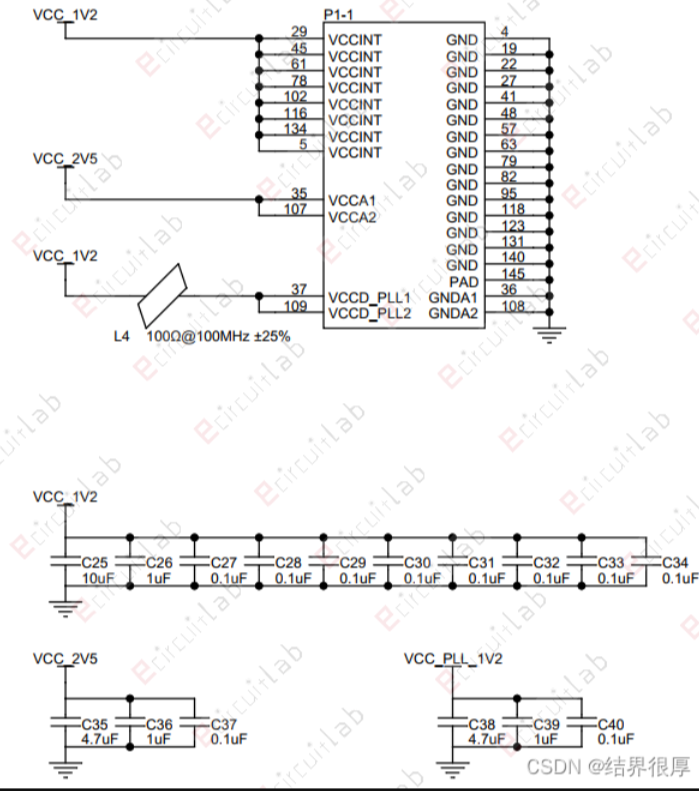

完成供电电源设计后,剩下就是处理接到FPGA的电源引脚上,1V电压接到VCCINT和VCCD_PLL上,对于VCCINT,每个电源IO放置一个0.1uF去耦电容,最后再在电源VCCINT的电源轨上放置10uF+1uF的组合即可。而对于VCCD_PLL,参考上面的描述,是需要放置一个磁珠跟VCCINT隔离的,这里选择100Ω/100M,额定电流900mA的磁珠进行隔离,对于去耦使用4.7uF+1uF+0.1uF的组合即可,而VCCA的2.5V直接接入,同样放置4.7uF+1uF+0.1uF的去耦组合即可,如下图所示。

图6. FPGA的VCCINT、VCCD_PLL、VCCA连接和去耦

对于VCCIO,上面说了电流不会很大,所以每个BANK放置一个0.1uF去耦即可,在我给出的参考设计中,VCCIO5和VCCIO6这两个BANK的VCCIO供电,我用了0Ω电阻设置3.3V和2.5V可选,目的是使电路支持使用LVDS信号,对于为什么要用这2个BANK,而不是其他BANK,我留在后续的文章中解释。剩下的其他BANK使用3.3V供电,如下。

2. 配置和烧录

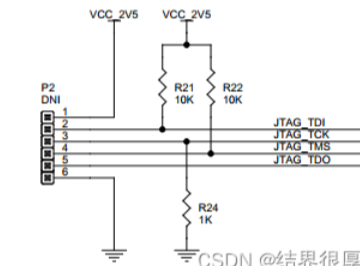

FPGA也跟MCU或者其他处理器一样,也需要设置对应的启动方式,也需要对应的烧录接口。对于烧录方式,设计使用JTAG烧录,对于JTAG信号处理,设计一一对应连上即可。JTAG的TMS、TDI两个信号需要上拉,上拉的电压注意下是2.5V,TCK需要下拉,这里我预留一个排针接口烧录如下。

图8. 通过排针使用JTAG烧录

FPGA不像市面上的很多MCU带有内置Flash,所以电路配置文件存储在外部的Flash中,对于外部配置文件的加载,

有多种加载方式,一般选用AS方式加载。

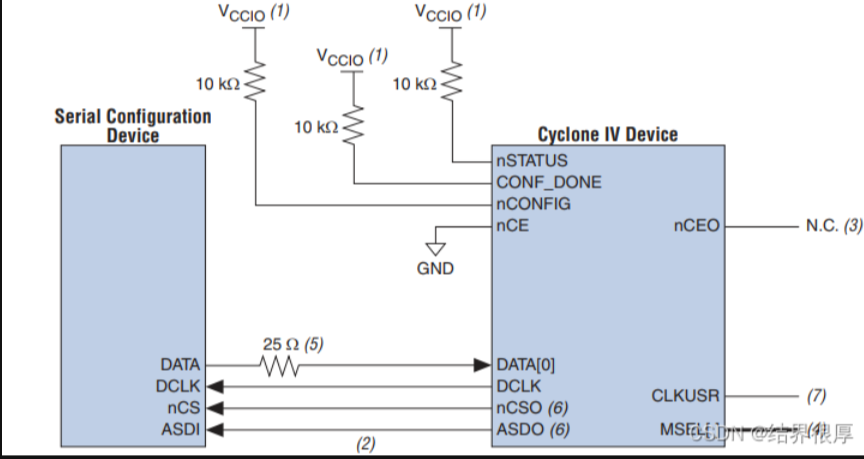

对于AS的加载配置方式,在官方手册上说明电路设置如下图所示,需要把nSTATUS、CONF_DONE、nCONFIG三个信号上拉至对应BANK的电压,nCE为片选信号需要下拉至GND。

图9. AS配置方式

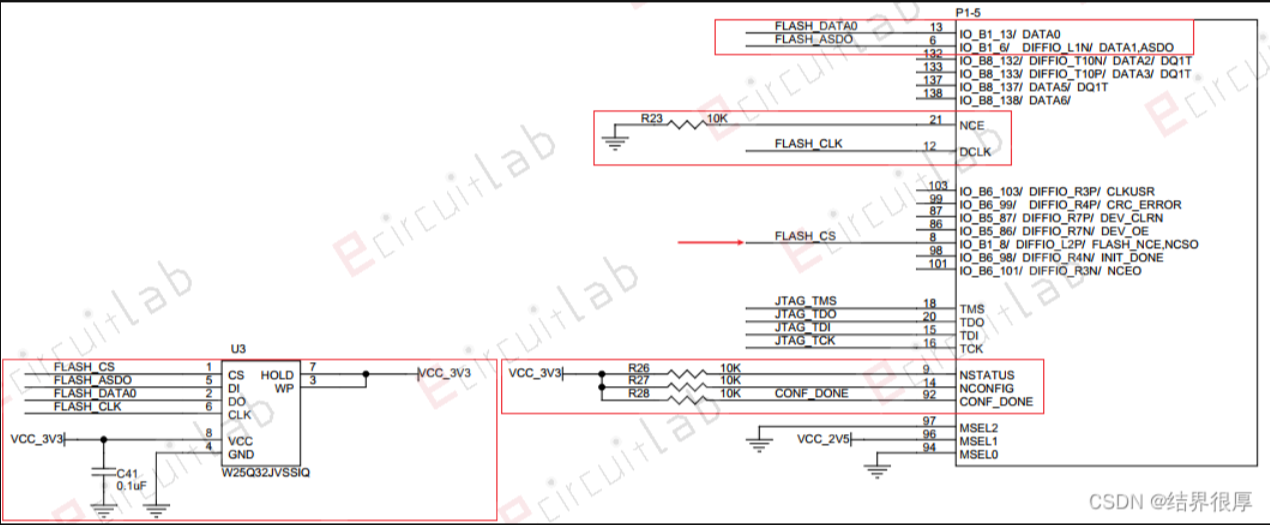

参考AS的配置参考电路处理设计电路如下,Flash选用W25Q32JVSSIQ,信号参考图9一一对应连接即可。

因为nSTATUS、CONF_DONE、nCONFIG三个信号都在BANK1上,前面设计BANK1供电电压为3.3V,所以均上拉至3.3V。

图10. AS配置方式的实际电路

选择FPGA的加载配置方式为AS方式后,除了上面的电路,还需要设置FPGA的MSEL引脚,选择适合的POR Delay和电压,否则FPGA也不能正常配置启动。

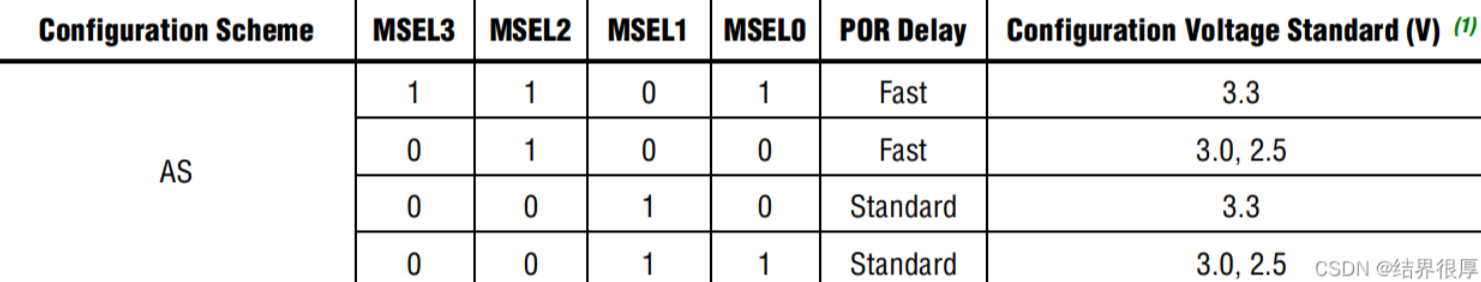

在FPGA的器件手册中描述了Cyclone IV E在AS模式时,MSEL的不同组合对应的不同设置如下图11所示。

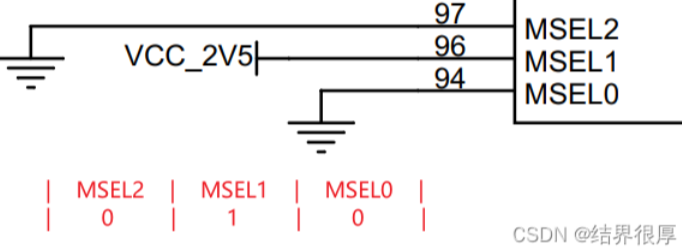

POR Delay可设置为Fast、Standard两种模式,这里设置为Standard模式,参考图10的AS电路电压为3.3V,所以需要把MSEL1信号拉高至对应的BANK电平,MSEL2和MSEL0接地,我们使用的型号没有MSEL3,可以不管。

图11. MSEL设置表

图12. 设置POR Delay为Standard模式,电压3.3V

3. 时钟和复位

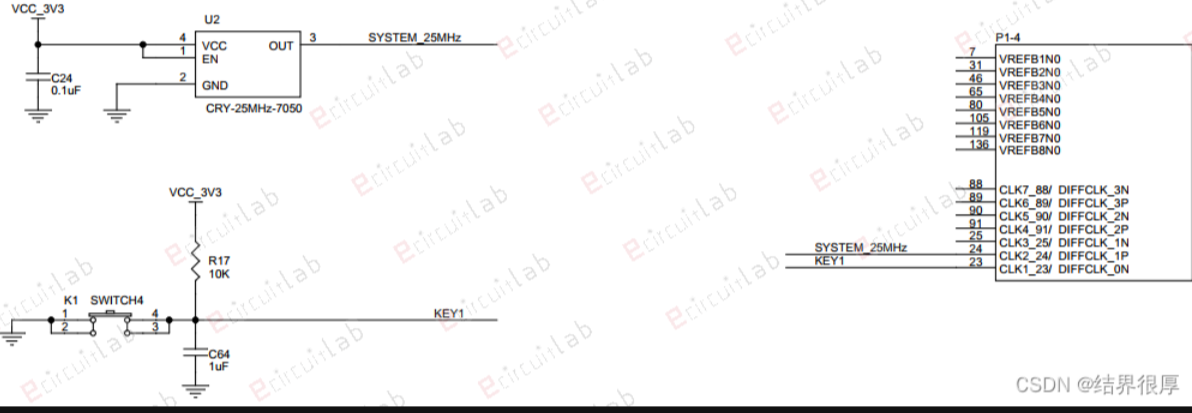

同样FPGA也需要时钟和复位,时钟跟MCU或者其他处理器的设计方式有点不一样,对于MCU或其他处理器,可以使用无源晶振作为时钟源,但FPGA不能,FPGA必须使用有源时钟作为参考时钟源,对于时钟频率没有要求,看具体的RTL工程需求,如果RTL工程没有特别需求,那就放置一个25MHz的有源时钟最佳,因为25MHz容易倍频和分频得到很多常用的外设时钟频率。

EP4CE6E22C8N有多个IO口可作为参考时钟输入,这里选择PIN_24作为参考时钟输入。

对于复位信号,这里使用简单的RC复位方式,预留按键可手动复位,复位信号通常选择通过任意的DIFFCLK_XN引脚接入,当然使用其他IO也可以,完整的时钟和复位电路参考设计如下。

图13. 时钟和复位参考电路

转自——–ecircuitlab